= MY-IMX6-CB140简介 =

MY-IMX6-CB140是我司基于NXP i.MX 6UltraLite应用处理器设计研发的嵌入式核心控制模块。核心板采用邮票孔的连接方式。

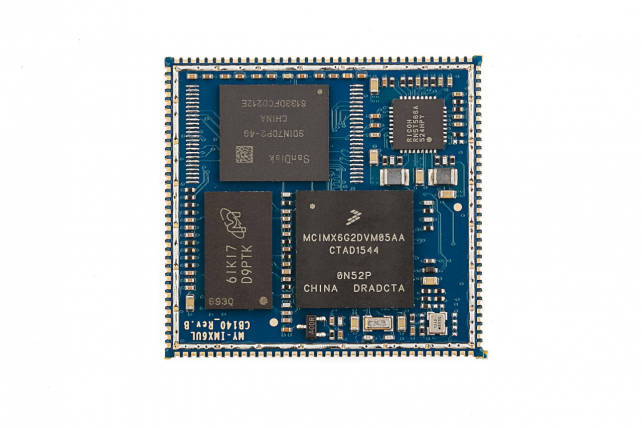

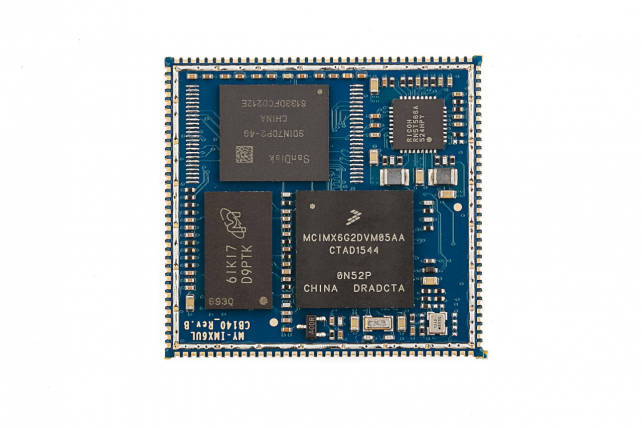

MY-IMX6-CB140视图

正面

背面

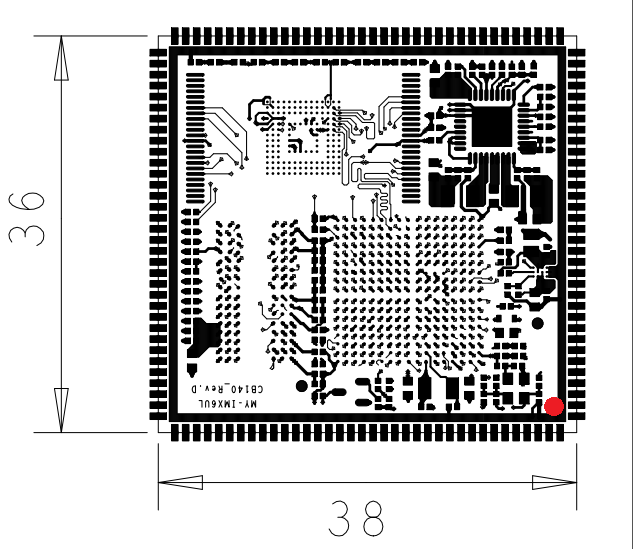

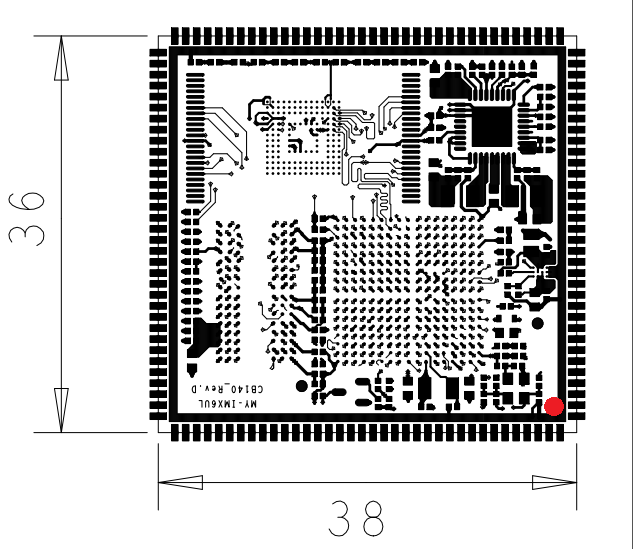

MY-IMX6-CB140尺寸

36mm * 38mm

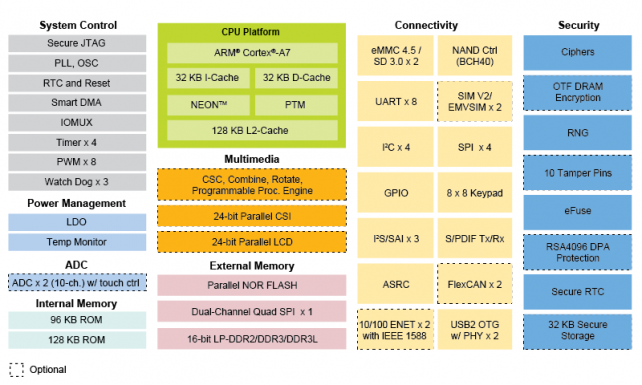

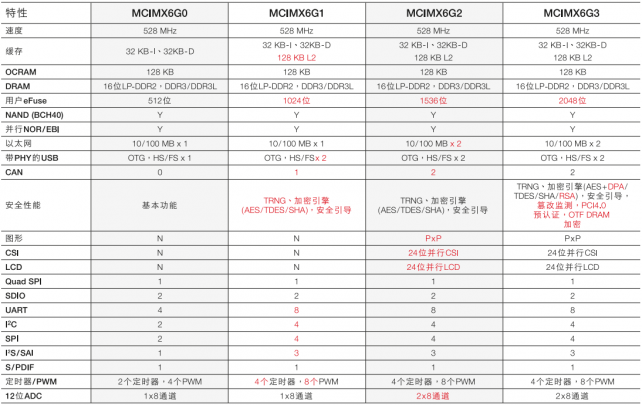

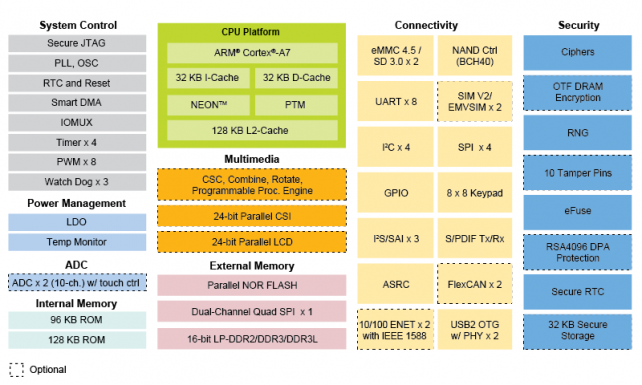

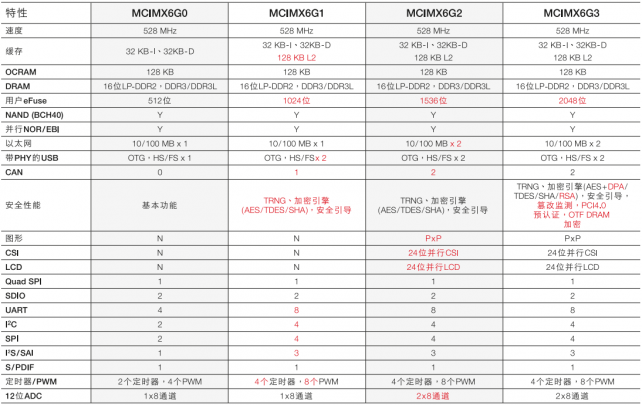

= i.MX 6UltraLite处理器介绍 =

框图及差异

概述

i.MX 6UltraLite扩展了i.MX6系列,它是一个高性能、超高效处理器系列,采用先进的ARM®Cortex®-A7内核,运行速度高达528 MHz。i.MX6UltraLite应用处理器包括一个集成的电源管理模块,降低了外接电源的复杂性,并简化了上电时序。这个系列的每个处理器提供多种存储器接口,其中包括16位LPDDR2、DDR3、DDR3L、原始和管理的NAND闪存、NOR闪存、eMMC、Quad SPI和各种其他接口,用于连接外围设备,如WLAN、Bluetooth™、GPS、显示器和摄像头传感器.

特性

- ARM® Cortex®-A7,运行频率528 MHz,128 KB L2缓存

- 并行LCD显示,分辨率高达WXGA (1366x768)

- 8/10/16/24位并行摄像头传感器接口

- 16位LP-DDR2, DDR3/DDR3L

- 8/16位并行NOR FLASH / PSRAM

- 双通道Quad-SPI NOR FLASH

- 8位原始NAND FLASH与40位ECC

- 两个MMC 4.5/SD 3.0/SDIO端口

- 两个USB 2.0 OTG,HS/FS,器件或主机,带PHY接口

- 音频接口包括3个I2S/SAI, S/PDIF Tx/Rx

- 两个10/100以太网,支持IEEE 1588协议

- 两个12位ADC,高达10个输入通道,以及电阻式触摸控制器(4线/5线)

- 部分PMU集成

- 安全模块:TRNG,加密引擎(带DPA的AES,TDES/ SHA/ RSA),防篡改监控,安全引导,SIMV2/ EVMSIM X 2,OTF DRAM加密,PCI4.0预认证

- 14x14 289MAPBGA 0.8mm间距

- 9x9 272 MAPBGA 0.5mm间距

MY-IMX6-CB140

== 硬件配置 ==

CPU

|

i.MX 6UltraLite

<thead>

| 兼容汽车,工业,消费级 |

</thead>

<tbody>

| 内存 |

| DDR3 256MB |

| 可扩展至512MB |

| - |

| 存储 |

| 4GB eMMC |

| 兼容至64GB |

| } |

</tbody>

供电电源

5V输入

温度范围

工作温度

0°C ~ 95°C

-40°C ~ 105°C

-40°C ~ 125°C

存储温度

-60°C ~ 125°C

操作系统支持

Linux

Linux-3.14.52

QT

QT5.5(使用Linux-3.14.52内核)

硬件默认接口

默认接口

| CCM

|

CCM_CLK1

|

支持

<thead>

| 外部时钟输出 |

</thead>

<tbody>

| PMIC_STBY_REQ |

| 支持 |

| 用于核心板 |

| - |

| rowspan=2|ECSPI |

| ECSPI1 |

| 支持 |

| 1个片选 |

| - |

| ECSPI2 |

| 支持 |

| 1个片选 |

| - |

| ENET |

| ENET1 |

| 支持 |

| 10/100-Mbps |

| - |

| rowspan=2|FLEXCAN |

| FLEXCAN1 |

| 支持 |

|

| - |

| FLEXCAN2 |

| 支持 |

|

| - |

| rowspan=3|GPIO |

| GPIO1 |

| 支持 |

| 2个用于SD1,2个用于ENET1 |

| - |

| GPIO4 |

| 支持 |

| 1个用于RTC |

| - |

| GPIO5 |

| 支持 |

| 9个用于通用GPIO,1个用于触摸 |

| - |

| rowspan=2|I2C |

| I2C1 |

| 支持 |

|

| - |

| I2C2 |

| 支持 |

|

| - |

| eLCDIF |

| LCDIF |

| 支持 |

| 24位 |

| - |

| rowspan=3|PWM |

| PWM2 |

| 支持 |

|

| - |

| PWM4 |

| 支持 |

| 用于LCD背光控制 |

| - |

| PWM5 |

| 支持 |

|

| - |

| JTAG |

| SJC |

| 支持 |

|

| - |

| rowspan=4|SRC |

| ONOFF |

| 支持 |

|

| - |

| POR_B |

| 支持 |

| 外部复位信号 |

| - |

| BOOT_MODE0 |

| 支持 |

| Boot模式控制 |

| - |

| BOOT_MODE1 |

| 支持 |

| Boot模式控制 |

| - |

| rowspan=8|UART |

| UART1 |

| 支持 |

| 可支持RS485 |

| - |

| UART2 |

| 支持 |

|

| - |

| UART3 |

| 支持 |

|

| - |

| UART4 |

| 支持 |

|

| - |

| UART5 |

| 支持 |

|

| - |

| UART6 |

| 支持 |

|

| - |

| UART7 |

| 支持 |

|

| - |

| UART8 |

| 支持 |

| 可支持RS485 |

| - |

| rowspan=2|USB |

| USB_OTG1 |

| 支持 |

| 用作USB OTG接口 |

| - |

| USB_OTG2 |

| 支持 |

| 用作USB HOST接口 |

| - |

| rowspan=2|uSDHC |

| uSDHC1 |

| 支持 |

| 4位 |

| - |

| uSHDC2 |

| 支持 |

| 8位,用于核心板的eMMC |

| - |

| WDOG |

| WDOG1 |

| 支持 |

|

| } |

</tbody>

接口说明

CCM(Clock Control Module):

These modules are responsible for clock.

ECSPI(Enhanced Configurable SPI):

Full-duplex enhanced Synchronous Serial Interface, with data rate up to 52 Mbit/s. It is configurable to support Master/Slave modes, four chip selects to support multiple peripherals.

ENET(Ethernet Controller):

The Ethernet Media Access Controller (MAC) is designed to support 10/100 Mbit/s Et hernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The module has dedicated hardware to support the IEEE 1588 standard.

FLEXCAN(Flexible Controller Area Network):

The CAN protocol was primarily, but not only, designed to be used as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the Electromagnetic interference (EMI) environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module is a full implementation of the CAN protocol specification, Version 2.0 B, which supports both standard and extended message frames.

GPIO(General Purpose I/O Modules):

Used for general purpose input/output to external ICs. Each GPIO module supports up to 32 bits of I/O.

LCDIF(LCD interface):

The LCDIF is a general purpose display controller used to drive a wide range of display devices varying in size and capability. The LCDIF is designed to support dumb (synchronous 24-bit Parallel RGB interface) and smart (asynchronous parallel MPU interface) LCD devices.

PWM(Pulse Width Modulation):

The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can al so generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.

SJC(System JTAG Controller):

The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6UltraLite processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards. The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities.

UART(UART Interface):

Each of the UART modules support the following serial data transmit/receive protocols and configurations:

• 7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)

• Programmable baud rates up to 5 Mbps.

• 32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud

uSDHC(Ultra Secured Digital Host Controller):

i.MX 6UltraLite specif ic SoC characteristics:

All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:

• Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.5/4.2/4.3/4.4/4.41/ including high-capacity (size > 2 GB) cards HC MMC.

• Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDXC cards up to 2 TB.

• Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v3.0

Two ports support:

• 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max)

• 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

• 4-bit or 8-bit transfer mode specifications for eMMC chips up to 200 MHz in HS200 mode (200 MB/s max)

USB(Universal Serial Bus 2.0):

USBO2 (USB OTG1 and USB OTG2) contains:

• Two high-speed OTG 2.0 modules with integrated HS USB PHYs

• Support eight Transmit (TX) and eight Receive (Rx) endpoints, including endpoint 0

WDOG(Watch Dog):

The Watch Dog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.

管脚定义

序号

|

引脚名称

|

信号名称

|

接口

|

功能

|

模式

<thead>

| 方向 |

</thead>

<tbody>

| 001 |

| CCM_CLK1_N |

| CLK1_N |

| CCM |

| ccm_clk1_n |

| - |

| - |

| - |

| 002 |

| CCM_CLK1_P |

| CLK1_P |

| CCM |

| ccm_clk1_p |

| - |

| - |

| - |

| 003 |

| GPIO1_IO08 |

| WDOG_B |

| WDOG1 |

| wdog_wdog_b |

| ALT1 |

| Input/Output |

| - |

| 004 |

| GPIO1_IO05 |

| PWM_4 |

| PWM4 |

| pwm_out |

| ALT1 |

| Output |

| - |

| 005 |

| GPIO1_IO09 |

| PWM_2 |

| PWM2 |

| pwm_out |

| ALT0 |

| Output |

| - |

| 006 |

| NAND_DQS |

| PWM_5 |

| PWM5 |

| pwm_out |

| ALT3 |

| Output |

| - |

| 007 |

| GPIO1_IO02 |

|USB_OTG2_PWR

(ENET_nRST) |

| GPIO1 |

| gpio_io2 |

| ALT5 |

| Input/Output |

| - |

| 008 |

| GPIO1_IO01 |

USB_OTG1_OC

(SD1_CD) |

| GPIO1 |

| gpio_io1 |

| ALT5 |

| Input/Output |

| - |

| 009 |

| GPIO1_IO04 |

USB_OTG1_PWR

(SD1_WP) |

| GPIO1 |

| gpio_io4 |

| ALT5 |

| Input/Output |

| - |

| 010 |

| GPIO1_IO03 |

USB_OTG2_OC

(ENET_nINT) |

| GPIO1 |

| gpio_io3 |

| ALT5 |

| Input/Output |

| - |

| 011 |

| UART2_RTS_B |

| CAN2_RX |

| FLEXCAN2 |

| can_rx |

| ALT2 |

| Input |

| - |

| 012 |

| UART2_CTS_B |

| CAN2_TX |

| FLEXCAN2 |

| can_tx |

| ALT2 |

| Output |

| - |

| 013 |

| UART3_RTS_B |

| CAN1_RX |

| FLEXCAN1 |

| can_rx |

| ALT2 |

| Input |

| - |

| 014 |

| UART3_CTS_B |

| CAN1_TX |

| FLEXCAN1 |

| can_tx |

| ALT2 |

| Output |

| - |

| 015 |

| GPIO1_IO07 |

| ENET_MDC |

| ENET1 |

| enet_mdc |

| ALT0 |

| Output |

| - |

| 016 |

| GPIO1_IO06 |

| ENET_MDIO |

| ENET1 |

| enet_mdio |

| ALT0 |

| Input/Output |

| - |

| 017 |

| ENET1_TX_DATA1 |

| ENET1_TXD1 |

| ENET1 |

| enet_tdata1 |

| ALT0 |

| Output |

| - |

| 018 |

| ENET1_TX_EN |

| ENET1_TXEN |

| ENET1 |

| enet_tx_en |

| ALT0 |

| Output |

| - |

| 019 |

| ENET1_RX_DATA0 |

| ENET1_RXD0 |

| ENET1 |

| enet_rdata0 |

| ALT0 |

| Input |

| - |

| 020 |

| ENET1_TX_DATA0 |

| ENET1_TXD0 |

| ENET1 |

| enet_tdata0 |

| ALT0 |

| Output |

| - |

| 021 |

| ENET1_RX_DATA1 |

| ENET1_RXD1 |

| ENET1 |

| enet_rdata1 |

| ALT0 |

| Input |

| - |

| 022 |

| ENET1_TX_CLK |

| ENET1_TX_CLK |

| ENET1 |

| enet_tx_clk |

| ALT0 |

| Input |

| - |

| 023 |

| ENET1_RX_EN |

| ENET1_CRS_DV |

| ENET1 |

| enet_rx_en |

| ALT0 |

| Input |

| - |

| 024 |

| ENET1_RX_ER |

| ENET1_RXER |

| ENET1 |

| enet_rx_er |

| ALT0 |

| Input |

| - |

| 025 |

| UART1_RX_DATA |

| UART1_RXD |

| UART1 |

| uart_rx |

| ALT0 |

| Input |

| - |

| 026 |

| UART1_CTS_B |

| UART1_CTS |

| UART1 |

| uart_cts_b |

| ALT0 |

| Output |

| - |

| 027 |

| UART1_TX_DATA |

| UART1_TXD |

| UART1 |

| uart_tx |

| ALT0 |

| Output |

| - |

| 028 |

| UART1_RTS_B |

| UART1_RTS |

| UART1 |

| uart_rts_b |

| ALT0 |

| Input |

| - |

| 029 |

| UART2_TX_DATA |

| UART2_TXD |

| UART2 |

| uart_tx |

| ALT0 |

| Output |

| - |

| 030 |

| UART2_RX_DATA |

| UART2_RXD |

| UART2 |

| uart_rx |

| ALT0 |

| Input |

| - |

| 031 |

| UART3_TX_DATA |

| UART3_TXD |

| UART3 |

| uart_tx |

| ALT0 |

| Output |

| - |

| 032 |

| UART3_RX_DATA |

| UART3_RXD |

| UART3 |

| uart_rx |

| ALT0 |

| Input |

| - |

| 033 |

| UART4_TX_DATA |

| UART4_TXD |

| UART4 |

| uart_tx |

| ALT0 |

| Output |

| - |

| 034 |

| UART4_RX_DATA |

| UART4_RXD |

| UART4 |

| uart_rx |

| ALT0 |

| Input |

| - |

| 035 |

| UART5_TX_DATA |

| UART5_TXD |

| UART5 |

| uart_tx |

| ALT0 |

| Output |

| - |

| 036 |

| UART5_RX_DATA |

| UART5_RXD |

| UART5 |

| uart_tx |

| ALT0 |

| Output |

| - |

| 037 |

| ENET2_RX_ER |

| UART8_CTS |

| UART8 |

| uart_cts_b |

| ALT1 |

| Output |

| - |

| 038 |

| ENET2_RX_DATA1 |

| UART6_TXD |

| UART6 |

| uart_tx |

| ALT1 |

| Output |

| - |

| 039 |

| ENET2_TX_CLK |

| UART8_RTS |

| UART8 |

| uart_rts_b |

| ALT1 |

| Input |

| - |

| 040 |

| ENET2_RX_DATA0 |

| UART6_RXD |

| UART6 |

| uart_rx |

| ALT1 |

| Input |

| - |

| 041 |

| ENET2_TX_EN |

| UART8_TXD |

| UART8 |

| uart_tx |

| ALT1 |

| Output |

| - |

| 042 |

| ENET2_RX_EN |

| UART7_TXD |

| UART7 |

| uart_tx |

| ALT1 |

| Output |

| - |

| 043 |

| ENET2_TX_DATA1 |

| UART8_RXD |

| UART8 |

| uart_rx |

| ALT1 |

| Input |

| - |

| 044 |

| ENET2_TX_DATA0 |

| UART7_RXD |

| UART7 |

| uart_rx |

| ALT1 |

| Input |

| - |

| 045 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 046 |

| - |

| 5V |

| - |

| - |

| - |

| - |

| - |

| 047 |

| - |

| 5V |

| - |

| - |

| - |

| - |

| - |

| 048 |

| - |

| 5V |

| - |

| - |

| - |

| - |

| - |

| 049 |

| - |

| DCDC_3V3 |

| - |

| - |

| - |

| - |

| - |

| 050 |

| - |

| VDD_SNVS_IN |

| - |

| - |

| - |

| Output |

| - |

| 051 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 052 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 053 |

| LCD_DATA23 |

| LCD_DATA23 |

| LCDIF |

| lcdif_data23 |

| ALT0 |

| Input/Output |

| - |

| 054 |

| LCD_DATA19 |

| LCD_DATA19 |

| LCDIF |

| lcdif_data19 |

| ALT0 |

| Input/Output |

| - |

| 055 |

| LCD_DATA20 |

| LCD_DATA20 |

| LCDIF |

| lcdif_data20 |

| ALT0 |

| Input/Output |

| - |

| 056 |

| LCD_DATA21 |

| LCD_DATA21 |

| LCDIF |

| lcdif_data21 |

| ALT0 |

| Input/Output |

| - |

| 057 |

| LCD_DATA22 |

| LCD_DATA22 |

| LCDIF |

| lcdif_data22 |

| ALT0 |

| Input/Output |

| - |

| 058 |

| LCD_DATA17 |

| LCD_DATA17 |

| LCDIF |

| lcdif_data17 |

| ALT0 |

| Input/Output |

| - |

| 059 |

| LCD_DATA18 |

| LCD_DATA18 |

| LCDIF |

| lcdif_data18 |

| ALT0 |

| Input/Output |

| - |

| 060 |

| LCD_DATA13 |

| LCD_DATA13 |

| LCDIF |

| lcdif_data13 |

| ALT0 |

| Input/Output |

| - |

| 061 |

| LCD_DATA14 |

| LCD_DATA14 |

| LCDIF |

| lcdif_data14 |

| ALT0 |

| Input/Output |

| - |

| 062 |

| LCD_DATA08 |

| LCD_DATA8 |

| LCDIF |

| lcdif_data8 |

| ALT0 |

| Input/Output |

| - |

| 063 |

| LCD_DATA09 |

| LCD_DATA9 |

| LCDIF |

| lcdif_data9 |

| ALT0 |

| Input/Output |

| - |

| 064 |

| LCD_DATA07 |

| LCD_DATA7 |

| LCDIF |

| lcdif_data7 |

| ALT0 |

| Input/Output |

| - |

| 065 |

| LCD_DATA06 |

| LCD_DATA6 |

| LCDIF |

| lcdif_data6 |

| ALT0 |

| Input/Output |

| - |

| 066 |

| LCD_DATA05 |

| LCD_DATA5 |

| LCDIF |

| lcdif_data5 |

| ALT0 |

| Input/Output |

| - |

| 067 |

| LCD_DATA04 |

| LCD_DATA4 |

| LCDIF |

| lcdif_data4 |

| ALT0 |

| Input/Output |

| - |

| 068 |

| LCD_DATA00 |

| LCD_DATA0 |

| LCDIF |

| lcdif_data0 |

| ALT0 |

| Input/Output |

| - |

| 069 |

| LCD_DATA01 |

| LCD_DATA1 |

| LCDIF |

| lcdif_data1 |

| ALT0 |

| Input/Output |

| - |

| 070 |

| LCD_DATA10 |

| LCD_DATA10 |

| LCDIF |

| lcdif_data10 |

| ALT0 |

| Input/Output |

| - |

| 071 |

| LCD_DATA15 |

| LCD_DATA15 |

| LCDIF |

| lcdif_data15 |

| ALT0 |

| Input/Output |

| - |

| 072 |

| LCD_DATA16 |

| LCD_DATA16 |

| LCDIF |

| lcdif_data16 |

| ALT0 |

| Input/Output |

| - |

| 073 |

| LCD_DATA12 |

| LCD_DATA12 |

| LCDIF |

| lcdif_data12 |

| ALT0 |

| Input/Output |

| - |

| 074 |

| LCD_DATA11 |

| LCD_DATA11 |

| LCDIF |

| lcdif_data11 |

| ALT0 |

| Input/Output |

| - |

| 075 |

| LCD_DATA03 |

| LCD_DATA3 |

| LCDIF |

| lcdif_data3 |

| ALT0 |

| Input/Output |

| - |

| 076 |

| LCD_DATA02 |

| LCD_DATA2 |

| LCDIF |

| lcdif_data2 |

| ALT0 |

| Input/Output |

| - |

| 077 |

| LCD_RESET |

| LCD_RESET |

| LCDIF |

| lcdif_reset |

| ALT0 |

| Input/Output |

| - |

| 078 |

| LCD_VSYNC |

| LCD_VSYNC |

| LCDIF |

| lcdif_vsync |

| ALT0 |

| Input |

| - |

| 079 |

| LCD_HSYNC |

| LCD_HSYNC |

| LCDIF |

| lcdif_hsync |

| ALT0 |

| Input |

| - |

| 080 |

| LCD_CLK |

| LCD_PCLK |

| LCDIF |

| lcdif_clk |

| ALT0 |

| Input |

| - |

| 081 |

| LCD_ENABLE |

| LCD_DE |

| LCDIF |

| lcdif_enable |

| ALT0 |

| Input/Output |

| - |

| 082 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 083 |

| CSI_PIXCLK |

| I2C1_SCL |

| I2C1 |

| i2c_scl |

| ALT3 |

| Input/Output |

| - |

| 084 |

| CSI_MCLK |

| I2C1_SDA |

| I2C1 |

| i2c_sda |

| ALT3 |

| Input/Output |

| - |

| 085 |

| NAND_CE1_B |

NAND_CE1N

(RTC_nRQ) |

| GPIO4 |

| gpio_io14 |

| ALT5 |

| Input/Output |

| - |

| 086 |

| SD1_CLK |

| SD1_CLK |

| uSDHC1 |

| usdhc_clk |

| ALT0 |

| Output |

| - |

| 087 |

| SD1_DATA3 |

| SD1_DATA3 |

| uSDHC1 |

| usdhc_data3 |

| ALT0 |

| Input/Output |

| - |

| 088 |

| SD1_DATA0 |

| SD1_DATA0 |

| uSDHC1 |

| usdhc_data0 |

| ALT0 |

| Input/Output |

| - |

| 089 |

| SD1_DATA1 |

| SD1_DATA1 |

| uSDHC1 |

| usdhc_data1 |

| ALT0 |

| Input/Output |

| - |

| 090 |

| SD1_DATA2 |

| SD1_DATA2 |

| uSDHC1 |

| usdhc_data2 |

| ALT0 |

| Input/Output |

| - |

| 091 |

| SD1_CMD |

| SD1_CMD |

| uSDHC1 |

| usdhc_cmd |

| ALT0 |

| Input/Output |

| - |

| 092 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 093 |

| CSI_DATA06 |

| ECSPI1_MOSI |

| ECSPI1 |

| ecspi_mosi |

| ALT3 |

| Input/Output |

| - |

| 094 |

| CSI_DATA02 |

| ECSPI2_MOSI |

| ECSPI2 |

| ecspi_mosi |

| ALT3 |

| Input/Output |

| - |

| 095 |

| CSI_DATA07 |

| ECSPI1_MISO |

| ECSPI1 |

| ecspi_miso |

| ALT3 |

| Input/Output |

| - |

| 096 |

| CSI_DATA04 |

| ECSPI1_SCLK |

| ECSPI1 |

| ecspi_sclk |

| ALT3 |

| Input/Output |

| - |

| 097 |

| CSI_DATA00 |

| ECSPI2_SCLK |

| ECSPI2 |

| ecspi_sclk |

| ALT3 |

| Input/Output |

| - |

| 098 |

| CSI_DATA05 |

| ECSPI1_CS0 |

| ECSPI1 |

| ecspi_ss0 |

| ALT3 |

| Output |

| - |

| 099 |

| CSI_DATA01 |

| ECSPI2_CS0 |

| ECSPI2 |

| ecspi_ss0 |

| ALT3 |

| Output |

| - |

| 100 |

| CSI_DATA03 |

| ECSPI2_MISO |

| ECSPI2 |

| ecspi_miso |

| ALT3 |

| Input/Output |

| - |

| 101 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 102 |

| CSI_HSYNC |

| I2C2_SCL |

| I2C2 |

| i2c_scl |

| ALT3 |

| Input/Output |

| - |

| 103 |

| CSI_VSYNC |

| I2C2_SDA |

| I2C2 |

| i2c_sda |

| ALT3 |

| Input/Output |

| - |

| 104 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 105 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 106 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 107 |

| SNVS_TAMPER5 |

SNVS_TAMPER5

(TOUCH_nEINT0) |

| GPIO5 |

| gpio_io5 |

| ALT5 |

| Input/Output |

| - |

| 108 |

| SNVS_TAMPER8 |

| SNVS_TAMPER8 |

| GPIO5 |

| gpio_io8 |

| ALT5 |

| Input/Output |

| - |

| 109 |

| SNVS_TAMPER1 |

| SNVS_TAMPER1 |

| GPIO5 |

| gpio_io1 |

| ALT5 |

| Input/Output |

| - |

| 110 |

| SNVS_TAMPER4 |

| SNVS_TAMPER4 |

| GPIO5 |

| gpio_io4 |

| ALT5 |

| Input/Output |

| - |

| 111 |

| SNVS_TAMPER3 |

| SNVS_TAMPER3 |

| GPIO5 |

| gpio_io3 |

| ALT5 |

| Input/Output |

| - |

| 112 |

| SNVS_TAMPER7 |

| SNVS_TAMPER7 |

| GPIO5 |

| gpio_io7 |

| ALT5 |

| Input/Output |

| - |

| 113 |

| SNVS_TAMPER0 |

| SNVS_TAMPER0 |

| GPIO5 |

| gpio_io0 |

| ALT5 |

| Input/Output |

| - |

| 114 |

| SNVS_TAMPER2 |

| SNVS_TAMPER2 |

| GPIO5 |

| gpio_io2 |

| ALT5 |

| Input/Output |

| - |

| 115 |

| SNVS_TAMPER6 |

| SNVS_TAMPER6 |

| GPIO5 |

| gpio_io6 |

| ALT5 |

| Input/Output |

| - |

| 116 |

| SNVS_TAMPER9 |

| SNVS_TAMPER9 |

| GPIO5 |

| gpio_io9 |

| ALT5 |

| Input/Output |

| - |

| 117 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 118 |

| SNVS_PMIC_ON_REQ |

| PMIC_ON_REQ |

| SNVS |

snvs_lp_wrapper

_pmic_on_req |

| ALT0 |

| Input |

| - |

| 119 |

| ONOFF |

| ONOFF |

| SRC |

| src_reset_b |

| ALT0 |

| Input |

| - |

| 120 |

| POR_B |

| POR_B |

| SRC |

| src_por_b |

| ALT0 |

| Input |

| - |

| 121 |

| BOOT_MODE1 |

| BOOT_MODE1 |

| SRC |

| src_boot_mode1 |

| ALT0 |

| Input |

| - |

| 122 |

| BOOT_MODE0 |

| BOOT_MODE0 |

| SRC |

| src_boot_mode0 |

| ALT0 |

| Input |

| - |

| 123 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 124 |

| USB_OTG2_VBUS |

| USB_OTG2_VBUS |

| USB |

| usb_otg2_vbus |

| - |

| - |

| - |

| 125 |

| USB_OTG2_DP |

| USB_OTG2_DP |

| USB |

| usb_otg2_dp |

| - |

| - |

| - |

| 126 |

| USB_OTG2_DN |

| USB_OTG2_DN |

| USB |

| usb_otg2_dn |

| - |

| - |

| - |

| 127 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 128 |

| USB_OTG1_VBUS |

| USB_OTG1_VBUS |

| USB |

| usb_otg1_vbus |

| - |

| - |

| - |

| 129 |

| USB_OTG1_DP |

| USB_OTG1_DP |

| USB |

| usb_otg1_dp |

| - |

| - |

| - |

| 130 |

| USB_OTG1_DN |

| USB_OTG1_DN |

| USB |

| usb_otg1_dn |

| - |

| - |

| - |

| 131 |

| - |

| GND |

| - |

| - |

| - |

| - |

| - |

| 132 |

| USB_OTG1_CHD_B |

| nUSB_OTG_CHD |

| USB |

| usb_otg1_chd_b |

| - |

| - |

| - |

| 133 |

| GPIO1_IO00 |

| USB_OTG1_ID |

| USB |

| usb_otg1_id |

| ALT2 |

| Input |

| - |

| 134 |

| JTAG_TRST_B |

| JTAG_nTRST |

| SJC |

| sjc_trstb |

| ALT0 |

| Input |

| - |

| 135 |

| JTAG_TMS |

| JTAG_TMS |

| SJC |

| sjc_tms |

| ALT0 |

| Input |

| - |

| 136 |

| JTAG_MOD |

| JTAG_MOD |

| SJC |

| sjc_mod |

| ALT0 |

| Input |

| - |

| 137 |

| JTAG_TCK |

| JTAG_TCK |

| SJC |

| sjc_tck |

| ALT0 |

| Input |

| - |

| 138 |

| JTAG_TDO |

| JTAG_TDO |

| SJC |

| sjc_tdo |

| ALT0 |

| Output |

| - |

| 139 |

| JTAG_TDI |

| JTAG_TDI |

| SJC |

| sjc_tdi |

| ALT0 |

| Input |

| - |

| 140 |

| - |

| GND |

| - |

| - |

| - |

| - |

| } |

</tbody>

|

|

|