MY-IMX6 底板设计指南

本文档是为了方便用户能够快速设计底板,本指南会针对客户经常碰见的问题做详细的讲解。确保客户设计的产品能够满足各种使用环境。

目录

= 电源 =

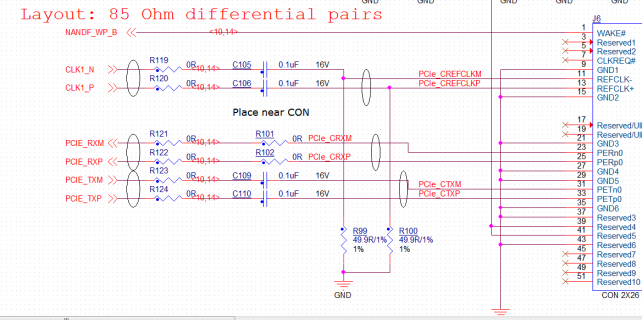

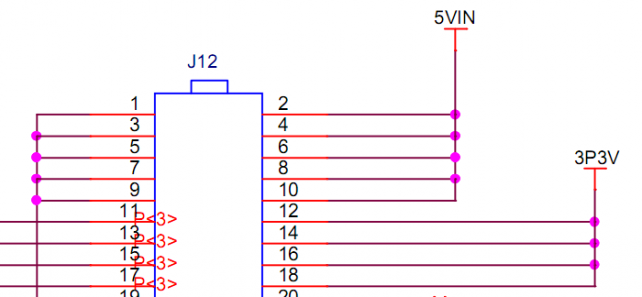

原理图

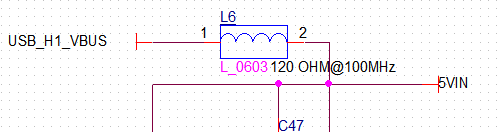

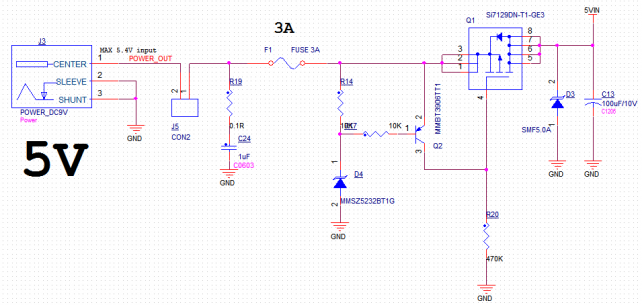

MY-I.MX6系列核心板,只需要一个5V电源(持续供电电流不低于2A,峰值2.5A-3A)输入即可。详见下图。

如果是直接的5V输入,5V的电源一定要做过压保护,过压保护电路参考如下。

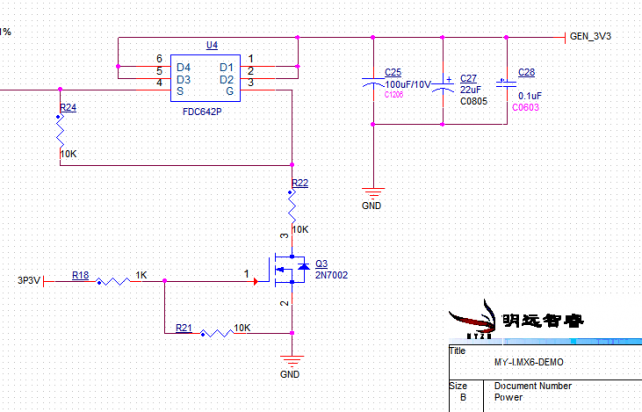

如果是高电压输入通过DCDC转换成5V,核心板会输出一个3P3V的电源,此电源的电流不超过500mA。如果底板上面3.3V的电流非常小,可以直接采用此3P3V作为底板的供电电源,如果用3P3V作为底板供电电源,请在3P3V电源上串上500mA的保险丝。

由于底板上面的3.3V电压通常会超过500mA,一般用户会单独通过DCDC或者LDO产生3.3V。

注意:底板的3.3V的电源,一定要通过核心板的3P3V来做使能控制,而不能够直接由底板上面的其他电源产生。如果底板上面还有其他电源,也必须有3P3V来做使能控制。此点是由于I.MX6芯片决定的。

参考电路如下:

PCB

核心板5V电源输入处要放置大的储能电容,确保CPU在瞬间增加负载的时候不至于断电。如果有过孔,确保过孔的电流至少能够通过3A的峰值电流,可以多打一些过孔增加电流。

= 串口设计 =

原理

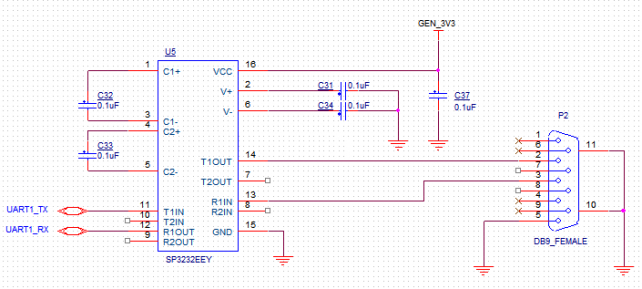

串口设计上面,经常会碰到的问题是RXD跟TXD的方向接反。参考原理图中的网标表示如下

TXD——CPU输出

RXD——CPU输入

PCB

注意:在设计底板的时候,我司提供了底板的原理图和PCB图,串口我司采用的是母头的接口。务必确保用户在设计的时候也使用的是母头,如果要更换成公头。RS232信号要更换。公头母头的详细信息请上网查询

= SD卡设计 =

原理

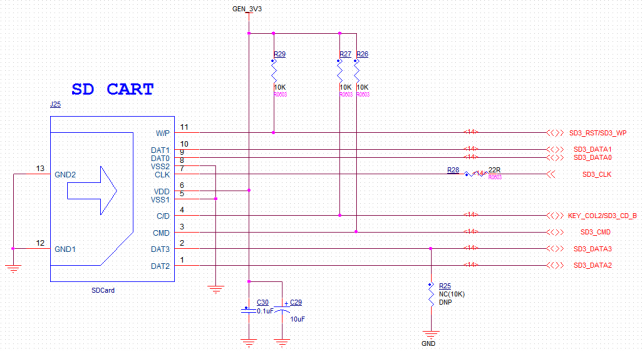

用户在设计SD卡的时候,针对IO的上下拉,请严格参考原理图,过多的上下拉可能会导致SD卡不能够正常的工作。参考图见下面

注意:如果用户不需要SD卡,要换成TF卡,由于TF卡是没有写保护这个功能的。写保护信号(SD3_RST/SD3_WP)要上拉,而不能够直接悬空。如果TF卡选用的是热插拔卡座,一定要清楚TF卡的检测管脚是哪个。一般情况是插卡之后,检测管脚接地,此时插入检测管脚(KEY_COL/SD3_CD_B)要上拉。如果TF卡选择的是翻盖式非可插拔卡座。写保护信号上拉,同时插入检测信号要接地(相当于始终插入了卡)

如果要增加ESD保护。确保接在SD_CLK信号上的ESD的电容值很小。

PCB

SD0,SD1,SD2,SD3,CMD,CLK信号要做等长处理。ESD原件要跟SD卡座非常接近。

= SATA设计 =

原理

SATA的原理相对简单,确保方向正确。由于一般SATA盘的电流比较大,5V输入电流要不低于3A为好。

PCB

SATA信号上面串联的4个电容要紧挨SATA座。

100欧姆的差分阻抗匹配

每组差分对之间的长度误差控制在±5mil

要求完整参考地平面

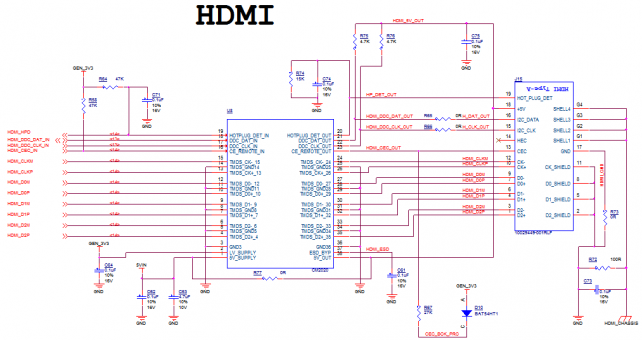

= HDMI =

原理

PCB

100欧姆差分阻抗匹配。

每组差分对之间的长度误差控制在±5mil

要求完整参考地平面

保护器件CM2020一定不要省略。

= LVDS =

原理

LVDS信号如果传输距离比较远,接的屏幕比较大,LVDS信号上面可以串联耦合磁珠,能够保证传输的质量更好。

PCB

100欧姆的差分阻抗匹配。

每组差分对之间的长度误差控制在±5mil

如果用双路LVDS信号做1080p的显示。LVDS0跟LVDS1的信号要做等长处理。

要求完整参考地平面

= RGB接口LCD =

原理

RGB接口的LCD满足24bit,18bit的接口模式