“MYZR-A40I-MB204 硬件介绍”的版本间的差异

| 第95行: | 第95行: | ||

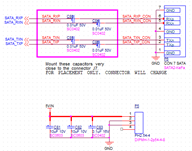

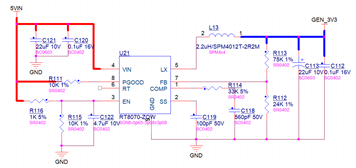

=='''底板电源'''== | =='''底板电源'''== | ||

底板使用DC 5.5插头(P22)插座插入5V电源供电,经过(P26)机械电源开关、自恢复保险丝(F1)、(D8)5.6V稳压二极管及Q7三极管通过电源输入反馈检测控制5VDC-DC(Q6)pin4 EN管脚高低电平输入,控制电源开启关闭以此来预防电源输入过压保护。后级输出5VIN电压经电容及磁珠滤波后依次分3.3V、1.8V降压给控制底板部分电路供电。<br> | 底板使用DC 5.5插头(P22)插座插入5V电源供电,经过(P26)机械电源开关、自恢复保险丝(F1)、(D8)5.6V稳压二极管及Q7三极管通过电源输入反馈检测控制5VDC-DC(Q6)pin4 EN管脚高低电平输入,控制电源开启关闭以此来预防电源输入过压保护。后级输出5VIN电压经电容及磁珠滤波后依次分3.3V、1.8V降压给控制底板部分电路供电。<br> | ||

| + | [[文件:MY-A40I-MB204_5V.png|480px]]<br> | ||

| + | [[文件:MY-A40I-MB204_3.3V.png|480px]]<br> | ||

| + | [[文件:MY-A40I-MB204_1.8V.png|480px]]<br> | ||

| − | + | 注意事项:电源部分设计时5V/3.3V请按照最低3A电流覆铜及电源走线,如需正反面走线需多打过孔,防止电源通电瞬间过载导致PCB烧板,保证供电正常。<br> | |

| − | 注意事项:电源部分设计时5V/3.3V请按照最低3A电流覆铜及电源走线,如需正反面走线需多打过孔,防止电源通电瞬间过载导致PCB烧板,保证供电正常。<br> | ||

=='''复位电路'''== | =='''复位电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_RESET.png|320px]]<br> | |

| − | 注意:本开发板只使用了图中的SW6复位开关,开门狗芯片未做验证所以不建议使用。<br> | + | 注意:本开发板只使用了图中的SW6复位开关,开门狗芯片未做验证所以不建议使用。<br> |

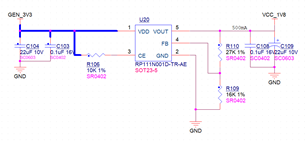

=='''按键电路'''== | =='''按键电路'''== | ||

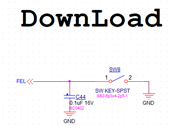

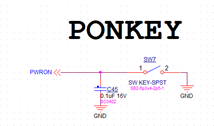

VOL+、VOL-、MENU、ENTER、HOME按键通过KEYADC0输入3.3V上拉不一样的电阻接地,做电平识别区分功能按键;DOWNLOAD、PWRON为单独按键,直接按下按键接地有效。<br> | VOL+、VOL-、MENU、ENTER、HOME按键通过KEYADC0输入3.3V上拉不一样的电阻接地,做电平识别区分功能按键;DOWNLOAD、PWRON为单独按键,直接按下按键接地有效。<br> | ||

| + | [[文件:MY-A40I-MB204_KEY.png|240px]] | ||

| + | [[文件:MY-A40I-MB204_DOWNLOAD.png|200px]] | ||

| + | [[文件:MY-A40I-MB204_PONKEY.png|240px]]<br> | ||

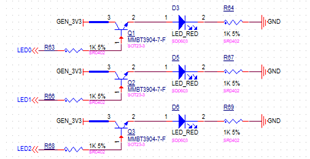

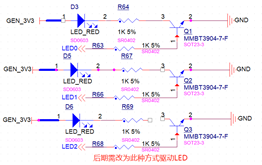

=='''LED显示'''== | =='''LED显示'''== | ||

| − | + | [[文件:MY-A40I-MB204_LED3.3V.png|400px]] | |

| + | [[文件:MY-A40I-MB204_LED5V.png|400px]]<br> | ||

注意:本系统配套3路LED 输出显示,建议后期上拉输入电源需由3.3V改为5V 输入并且将驱动方式改为后图电路,以防止驱动电压较高的LED 亮度不够。<br> | 注意:本系统配套3路LED 输出显示,建议后期上拉输入电源需由3.3V改为5V 输入并且将驱动方式改为后图电路,以防止驱动电压较高的LED 亮度不够。<br> | ||

=='''RTC实时时钟电路'''== | =='''RTC实时时钟电路'''== | ||

| − | + | 本电路所用RTC芯片内置晶振匹配电容,如需更换方案则需注意晶振精度问题,可在晶振两网络上并联匹配电容到地以达到调整精度的需要。 在底板上电时,底板的3.3V电源将给RTC芯片供电并给电池BT1充电;在底板掉电时,电池BT1将放电充当RTC芯片工作的电源。<br> | |

| − | + | [[文件:MY-A40I-MB204_RTC.png|480px]]<br> | |

=='''外接TF卡电路'''== | =='''外接TF卡电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_TF1.png|320px]] | |

| − | 注意:图中右侧接上拉电阻的SDIO接口网络,PCB设计时需做等长处理并要求3W间距且做整体包地处理。后续设计开发时候请针对SDCO 7条信号线均接上拉电阻。<br> | + | [[文件:MY-A40I-MB204_TF2.png|320px]]<br> |

| + | 注意:图中右侧接上拉电阻的SDIO接口网络,PCB设计时需做等长处理并要求3W间距且做整体包地处理。后续设计开发时候请针对SDCO 7条信号线均接上拉电阻。<br> | ||

=='''以太网电路接口'''== | =='''以太网电路接口'''== | ||

| − | + | [[文件:MY-A40I-MB204_ETH.png|480px]]<br> | |

| − | 注意:要求ETH TX/RX信号线PCB设计时需做等长处理并要求3W间距且做整体包地处理,差分对与其他网络要保持3倍线宽以上间距;差分对内要求等长误差范围在5mil以内,差分对间要求等长误差范围在25mil以内,电源部分需加粗滤波电容尽量靠近接线端。<br> | + | 注意:要求ETH TX/RX信号线PCB设计时需做等长处理并要求3W间距且做整体包地处理,差分对与其他网络要保持3倍线宽以上间距;差分对内要求等长误差范围在5mil以内,差分对间要求等长误差范围在25mil以内,电源部分需加粗滤波电容尽量靠近接线端。<br> |

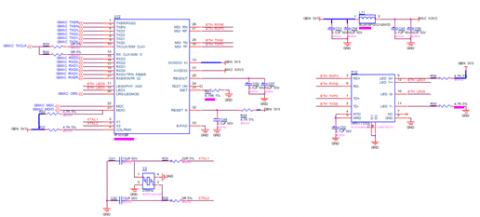

=='''USB电路'''== | =='''USB电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_USB1.png|480px]]<br> | |

| + | [[文件:MY-A40I-MB204_USB2.png|480px]]<br> | ||

注意:5VIN电源需严格预留最少1.5A通过电流设计加粗,DP/DM 信号线需走差分信号线。BR2/3是保护器件防静电、L5/6/8为共模滤波器,设计PCB时需要靠近USB接口, P9 为USB2.0插座可外接U盘或鼠标等。<br> | 注意:5VIN电源需严格预留最少1.5A通过电流设计加粗,DP/DM 信号线需走差分信号线。BR2/3是保护器件防静电、L5/6/8为共模滤波器,设计PCB时需要靠近USB接口, P9 为USB2.0插座可外接U盘或鼠标等。<br> | ||

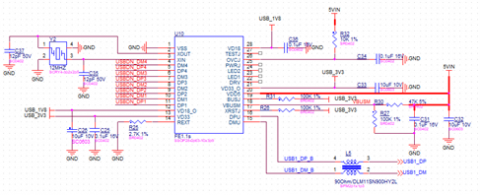

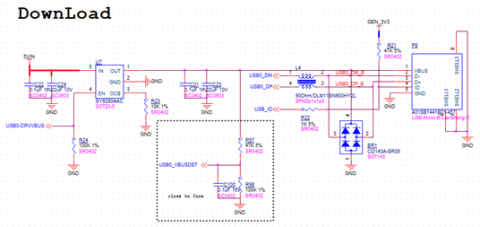

=='''DownLoad烧录系统USB口电路'''== | =='''DownLoad烧录系统USB口电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_Download-USB.png|480px]]<br> | |

此接口是Micro USB接口,用来接上位PC机给本开发板烧录系统。图中USB接口的ID引脚需上拉,不可接低电平;BR1是保护器件防静电,L4为共模滤波器,设计PCB时需要靠近Micro USB接口; USB线要求差分等长走线。<br> | 此接口是Micro USB接口,用来接上位PC机给本开发板烧录系统。图中USB接口的ID引脚需上拉,不可接低电平;BR1是保护器件防静电,L4为共模滤波器,设计PCB时需要靠近Micro USB接口; USB线要求差分等长走线。<br> | ||

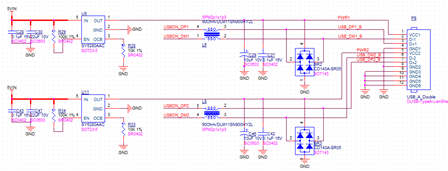

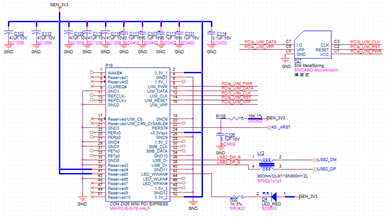

=='''4G模块电路'''== | =='''4G模块电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_4G.png|480px]]<br> | |

| − | 注意:4G模块瞬时工作电流可达3A 左右,电路设计时3.3v电源线需严格按照电流设计,滤波电容需尽量靠近放置;D4为模块的工作状态指示灯,P27S为SIM卡卡座要求靠近4G模块放置,模块到SIM卡网络要求成组走线避免走线太远长度误差太大并远离强信号干扰源和走线需就近布置。L12为共模滤波器,USB线要求差分走线。<br> | + | 注意:4G模块瞬时工作电流可达3A 左右,电路设计时3.3v电源线需严格按照电流设计,滤波电容需尽量靠近放置;D4为模块的工作状态指示灯,P27S为SIM卡卡座要求靠近4G模块放置,模块到SIM卡网络要求成组走线避免走线太远长度误差太大并远离强信号干扰源和走线需就近布置。L12为共模滤波器,USB线要求差分走线。<br> |

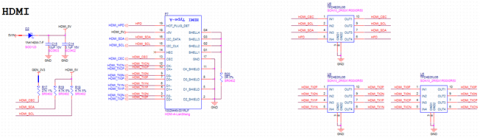

=='''HDMI 显示电路'''== | =='''HDMI 显示电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_HDMI.png|480px]]<br> | |

| − | 注意:U4/5/6 为TVS 静电保护管,PCB设计时尽量靠近HDMI 插口放置,除电源线外其余信号线需要按照差分规则走线并做差分对内等长,差分对与其他网络要保持3倍线宽以上间距,差分对内要求等长误差范围在5mil以内,差分对间要求等长误差范围在15mil以内。HDMI_CEC / HDMI_SDA/ HDMI_SCL 需严格按照电路图有效上拉。 | + | 注意:U4/5/6 为TVS 静电保护管,PCB设计时尽量靠近HDMI 插口放置,除电源线外其余信号线需要按照差分规则走线并做差分对内等长,差分对与其他网络要保持3倍线宽以上间距,差分对内要求等长误差范围在5mil以内,差分对间要求等长误差范围在15mil以内。HDMI_CEC / HDMI_SDA/ HDMI_SCL 需严格按照电路图有效上拉。 |

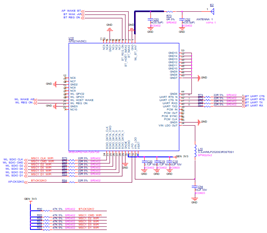

=='''RGB/LVDS/DSI 电路'''== | =='''RGB/LVDS/DSI 电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_RGB-LVDS.png|480px]] | |

| − | 注意:5V/3.3V 电源需按照1A以上电流设计,除电源线外其余信号线需严格按照等距差分信号线布线,信号线需按组分并行走线,走线尽量要短。 | + | [[文件:MY-A40I-MB204_DSI.png|240px]]<br> |

| + | 注意:5V/3.3V 电源需按照1A以上电流设计,除电源线外其余信号线需严格按照等距差分信号线布线,信号线需按组分并行走线,走线尽量要短。 | ||

=='''WIFI &蓝牙模块电路'''== | =='''WIFI &蓝牙模块电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_WIFI.png|480px]]<br> | |

| − | 注意: 3.3V 电源需按照1.5A以上电流设计,信号线电路需严格按原理图上拉,SDIO网络组等长走线,芯片pin1 WL_BT_ANY输出信号端输出线尽量加宽, E1所在网络要求走线满足50Ω阻抗设计,走线尽量短且不可走折角C93/R73/C92等器件需尽量靠近并π型输出,天线输出两端尽量覆铜GND包裹。<br> | + | 注意: 3.3V 电源需按照1.5A以上电流设计,信号线电路需严格按原理图上拉,SDIO网络组等长走线,芯片pin1 WL_BT_ANY输出信号端输出线尽量加宽, E1所在网络要求走线满足50Ω阻抗设计,走线尽量短且不可走折角C93/R73/C92等器件需尽量靠近并π型输出,天线输出两端尽量覆铜GND包裹。<br> |

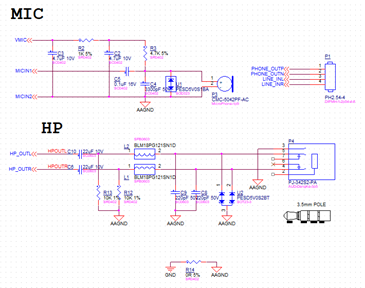

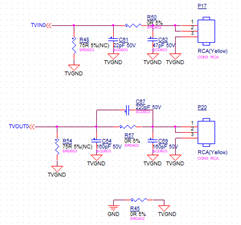

=='''MIC/HP/TVIN/TVOUT 电路'''== | =='''MIC/HP/TVIN/TVOUT 电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_MIC-HP.png|480px]]<br> | |

| − | 注意:MIC 及HP 走线下面需掏空不覆铜走线,两组AAGND及TVGND地需增加电阻串联来与GND隔离分开。麦克风与耳机等模拟信号的走线要求加粗到10mil以上,走线要平滑,最好包地处理,远离信号线等干扰。<br> | + | [[文件:MY-A40I-MB204_TVIN-TVOUT.png|480px]]<br> |

| + | 注意:MIC 及HP 走线下面需掏空不覆铜走线,两组AAGND及TVGND地需增加电阻串联来与GND隔离分开。麦克风与耳机等模拟信号的走线要求加粗到10mil以上,走线要平滑,最好包地处理,远离信号线等干扰。<br> | ||

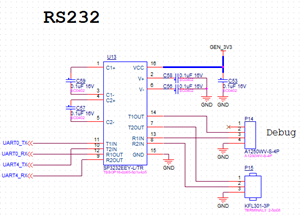

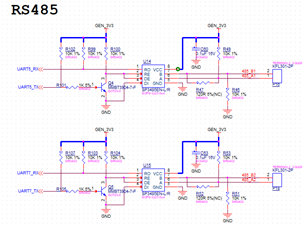

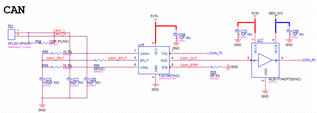

=='''RS232/485/CAN 电路'''== | =='''RS232/485/CAN 电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_RS232.png|320px]]<br> | |

| + | [[文件:MY-A40I-MB204_RS485.png|320px]]<br> | ||

| + | [[文件:MY-A40I-MB204_CAN.png|480px]]<br> | ||

注意: 3.3V 电源需按照1A以上电流设计,TX/RX信号线电路需严格按等距差分信号线布线。P14为内部调试端口为方便后期调试请用户在自行设计底板时将此调试串口引出。485信号端匹配电阻R47/R52视负载数量及传输长度增加120欧姆电阻。器件布局时U16、U17两芯片靠近P21接口摆放。<br> | 注意: 3.3V 电源需按照1A以上电流设计,TX/RX信号线电路需严格按等距差分信号线布线。P14为内部调试端口为方便后期调试请用户在自行设计底板时将此调试串口引出。485信号端匹配电阻R47/R52视负载数量及传输长度增加120欧姆电阻。器件布局时U16、U17两芯片靠近P21接口摆放。<br> | ||

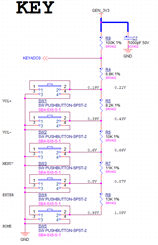

=='''SATA接口电路'''== | =='''SATA接口电路'''== | ||

| − | + | [[文件:MY-A40I-MB204_SATA.png|480px]]<br> | |

| − | 注意:设计PCB时,每路IIC两信号线应成组走线,避免走线太远时导致组内两网络走线长度误差太大。 | + | 注意:设计PCB时,每路IIC两信号线应成组走线,避免走线太远时导致组内两网络走线长度误差太大。 |

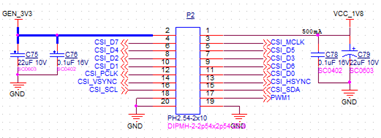

=='''CSI(DVP)接口电路'''== | =='''CSI(DVP)接口电路'''== | ||

| − | |||

P2端口为核心板引出预留IO, 输出信号线需以组为单位尽量走短及差分等长走线。3.3V/1.8V电路电流需按500mA以上设计。 | P2端口为核心板引出预留IO, 输出信号线需以组为单位尽量走短及差分等长走线。3.3V/1.8V电路电流需按500mA以上设计。 | ||

| + | [[文件:MY-A40I-MB204_CSI.png|480px]]<br> | ||

=='''IIC并联及核心板连接电路'''== | =='''IIC并联及核心板连接电路'''== | ||

| − | |||

一路IIC总线可挂载多路设备,预留0欧姆电阻供调试使用。每路IIC总线都应接上拉电阻到逻辑电平,使信号线不悬空并加强驱动能力。 设计PCB时,每路IIC两信号线应成组走线,避免走线太远时导致组内两网络走线长度误差太大。<br> | 一路IIC总线可挂载多路设备,预留0欧姆电阻供调试使用。每路IIC总线都应接上拉电阻到逻辑电平,使信号线不悬空并加强驱动能力。 设计PCB时,每路IIC两信号线应成组走线,避免走线太远时导致组内两网络走线长度误差太大。<br> | ||

核心板电源部分5V供电需预留3A电流电流覆铜及电源走线,如需正反面走线需多打过孔,防止电源通电瞬间过载导致PCB烧板,保证供电正常。滤波电容需就近放置,输出信号线需以组为单位尽量走短及差分等长走线。<br> | 核心板电源部分5V供电需预留3A电流电流覆铜及电源走线,如需正反面走线需多打过孔,防止电源通电瞬间过载导致PCB烧板,保证供电正常。滤波电容需就近放置,输出信号线需以组为单位尽量走短及差分等长走线。<br> | ||

| − | + | [[文件:MY-A40I-MB204_IIC.png|480px]]<br> | |

</div> | </div> | ||

2022年4月8日 (五) 11:15的版本

目录

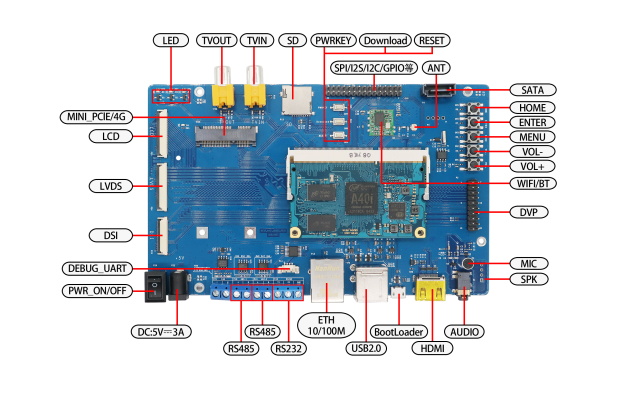

接口概览

正面图

背面图

MYZR_A40I_MB204底板参数

| 标号 | 接口 | 数量及功能 | 丝印 |

|---|---|---|---|

| 1 | Ethernet | 1个10/100M以太网,RJ45插座 | |

| 2 | UART | 1个,PCIE接口引出 | |

| 3 | 4G模块 | 1个,PCIE接口引出 | |

| 4 | sim卡 | 1个,座子引出 | |

| 5 | IO口 | 若干,排针引出 | |

| 6 | TF卡 | 1个,座子引出 | |

| 7 | USB2.0 | 2个,座子引出 | |

| 8 | 电源 | 5V恒压电源接口 | |

| 9 | HDMI接口 | 1个 | |

| 10 | LVDS接口 | 1个,FPC座子引出 | |

| 11 | MIPI_TX接口 | 1个,FPC座子引出 | |

| 12 | RGB屏接口 | 1个,FPC座子引出 | |

| 13 | LED灯 | 3个 | |

| 14 | WIFI&蓝牙模块 | 1个,USB接口 | |

| 15 | Micro_USB接口 | 1个,烧录用 | |

| 16 | SATA接口 | 1个 | |

| 17 | DVP接口 | 1个,插针引出 | |

| 18 | Audio | 1路PHONE,1路MIC,1路SPEAKER | |

| 19 | 复位按键 | 1个 | |

| 20 | 下载按键 | 1个 | |

| 21 | 唤醒按键 | 1个 | |

| 22 | 用户按键 | 5个 | |

| 23 | RTC | 1个,外部实时时钟 | |

| 24 | I2C | 1个,排针引出 | |

| 25 | SPI | 1个,排针引出 | |

| 26 | ADC | 1个,排针引出 |

A40I底板说明

底板电源

底板使用DC 5.5插头(P22)插座插入5V电源供电,经过(P26)机械电源开关、自恢复保险丝(F1)、(D8)5.6V稳压二极管及Q7三极管通过电源输入反馈检测控制5VDC-DC(Q6)pin4 EN管脚高低电平输入,控制电源开启关闭以此来预防电源输入过压保护。后级输出5VIN电压经电容及磁珠滤波后依次分3.3V、1.8V降压给控制底板部分电路供电。

注意事项:电源部分设计时5V/3.3V请按照最低3A电流覆铜及电源走线,如需正反面走线需多打过孔,防止电源通电瞬间过载导致PCB烧板,保证供电正常。

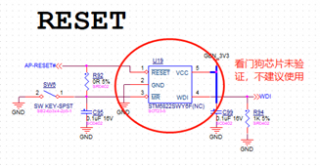

复位电路

注意:本开发板只使用了图中的SW6复位开关,开门狗芯片未做验证所以不建议使用。

按键电路

VOL+、VOL-、MENU、ENTER、HOME按键通过KEYADC0输入3.3V上拉不一样的电阻接地,做电平识别区分功能按键;DOWNLOAD、PWRON为单独按键,直接按下按键接地有效。

LED显示

注意:本系统配套3路LED 输出显示,建议后期上拉输入电源需由3.3V改为5V 输入并且将驱动方式改为后图电路,以防止驱动电压较高的LED 亮度不够。

RTC实时时钟电路

本电路所用RTC芯片内置晶振匹配电容,如需更换方案则需注意晶振精度问题,可在晶振两网络上并联匹配电容到地以达到调整精度的需要。 在底板上电时,底板的3.3V电源将给RTC芯片供电并给电池BT1充电;在底板掉电时,电池BT1将放电充当RTC芯片工作的电源。

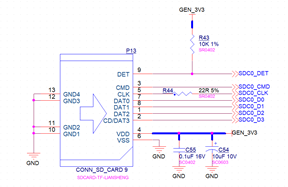

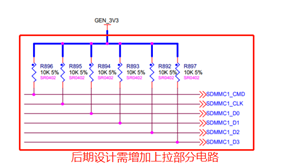

外接TF卡电路

注意:图中右侧接上拉电阻的SDIO接口网络,PCB设计时需做等长处理并要求3W间距且做整体包地处理。后续设计开发时候请针对SDCO 7条信号线均接上拉电阻。

以太网电路接口

注意:要求ETH TX/RX信号线PCB设计时需做等长处理并要求3W间距且做整体包地处理,差分对与其他网络要保持3倍线宽以上间距;差分对内要求等长误差范围在5mil以内,差分对间要求等长误差范围在25mil以内,电源部分需加粗滤波电容尽量靠近接线端。

USB电路

注意:5VIN电源需严格预留最少1.5A通过电流设计加粗,DP/DM 信号线需走差分信号线。BR2/3是保护器件防静电、L5/6/8为共模滤波器,设计PCB时需要靠近USB接口, P9 为USB2.0插座可外接U盘或鼠标等。

DownLoad烧录系统USB口电路

此接口是Micro USB接口,用来接上位PC机给本开发板烧录系统。图中USB接口的ID引脚需上拉,不可接低电平;BR1是保护器件防静电,L4为共模滤波器,设计PCB时需要靠近Micro USB接口; USB线要求差分等长走线。

4G模块电路

注意:4G模块瞬时工作电流可达3A 左右,电路设计时3.3v电源线需严格按照电流设计,滤波电容需尽量靠近放置;D4为模块的工作状态指示灯,P27S为SIM卡卡座要求靠近4G模块放置,模块到SIM卡网络要求成组走线避免走线太远长度误差太大并远离强信号干扰源和走线需就近布置。L12为共模滤波器,USB线要求差分走线。

HDMI 显示电路

注意:U4/5/6 为TVS 静电保护管,PCB设计时尽量靠近HDMI 插口放置,除电源线外其余信号线需要按照差分规则走线并做差分对内等长,差分对与其他网络要保持3倍线宽以上间距,差分对内要求等长误差范围在5mil以内,差分对间要求等长误差范围在15mil以内。HDMI_CEC / HDMI_SDA/ HDMI_SCL 需严格按照电路图有效上拉。

RGB/LVDS/DSI 电路

注意:5V/3.3V 电源需按照1A以上电流设计,除电源线外其余信号线需严格按照等距差分信号线布线,信号线需按组分并行走线,走线尽量要短。

WIFI &蓝牙模块电路

注意: 3.3V 电源需按照1.5A以上电流设计,信号线电路需严格按原理图上拉,SDIO网络组等长走线,芯片pin1 WL_BT_ANY输出信号端输出线尽量加宽, E1所在网络要求走线满足50Ω阻抗设计,走线尽量短且不可走折角C93/R73/C92等器件需尽量靠近并π型输出,天线输出两端尽量覆铜GND包裹。

MIC/HP/TVIN/TVOUT 电路

注意:MIC 及HP 走线下面需掏空不覆铜走线,两组AAGND及TVGND地需增加电阻串联来与GND隔离分开。麦克风与耳机等模拟信号的走线要求加粗到10mil以上,走线要平滑,最好包地处理,远离信号线等干扰。

RS232/485/CAN 电路

注意: 3.3V 电源需按照1A以上电流设计,TX/RX信号线电路需严格按等距差分信号线布线。P14为内部调试端口为方便后期调试请用户在自行设计底板时将此调试串口引出。485信号端匹配电阻R47/R52视负载数量及传输长度增加120欧姆电阻。器件布局时U16、U17两芯片靠近P21接口摆放。

SATA接口电路

注意:设计PCB时,每路IIC两信号线应成组走线,避免走线太远时导致组内两网络走线长度误差太大。

CSI(DVP)接口电路

P2端口为核心板引出预留IO, 输出信号线需以组为单位尽量走短及差分等长走线。3.3V/1.8V电路电流需按500mA以上设计。

IIC并联及核心板连接电路

一路IIC总线可挂载多路设备,预留0欧姆电阻供调试使用。每路IIC总线都应接上拉电阻到逻辑电平,使信号线不悬空并加强驱动能力。 设计PCB时,每路IIC两信号线应成组走线,避免走线太远时导致组内两网络走线长度误差太大。

核心板电源部分5V供电需预留3A电流电流覆铜及电源走线,如需正反面走线需多打过孔,防止电源通电瞬间过载导致PCB烧板,保证供电正常。滤波电容需就近放置,输出信号线需以组为单位尽量走短及差分等长走线。