MYZR-A40I-MB204 Hardware Introduction

目录

- 1 Overview of interfaces

- 2 A40I Bottom Plate Description

- 2.1 Bottom plate Power

- 2.2 Reset circuit

- 2.3 Button circuit

- 2.4 LED display

- 2.5 RTC real-time clock circuit

- 2.6 External TF card circuit

- 2.7 Ethernet circuit interface

- 2.8 USB circuit

- 2.9 DownLoad burns the system USB port circuit

- 2.10 4G module circuit

- 2.11 HDMI display circuit

- 2.12 RGB/LVDS/DSI circuits

- 2.13 WIFI &Bluetooth module circuit

- 2.14 MIC/HP/TVIN/TVOUT circuit

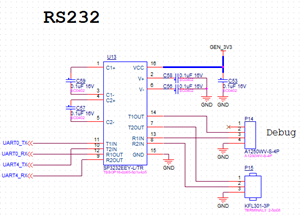

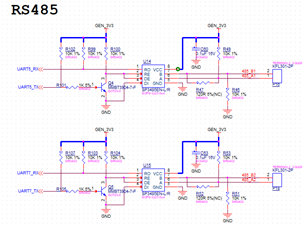

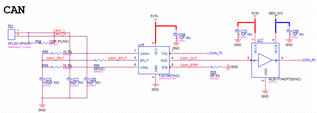

- 2.15 RS232/485/CAN circuit

- 2.16 SATA interface circuit

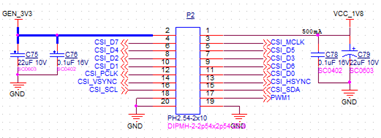

- 2.17 CSI (DVP) interface circuit

- 2.18 IIC parallel and core board connection circuit

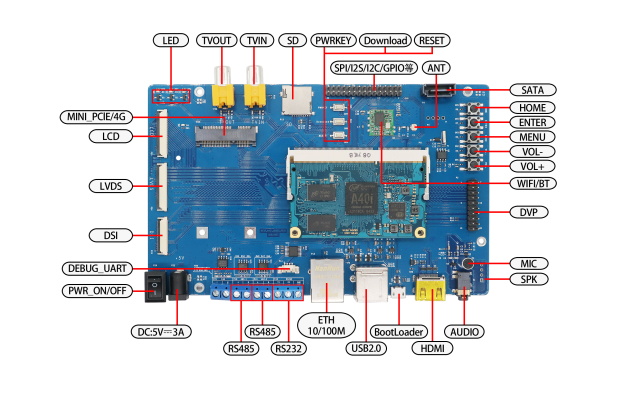

Overview of interfaces

Front view

Rear view

MYZR_A40I_MB204 Baseplate parameters

| Number | Interface | Features | Interface form | Silkscreen |

|---|---|---|---|---|

| 1 | 5V_IN | power input | DC-005 round mouth | P26 |

| 2 | Ethernet | one 10/100M Ethernet | RJ45 | P12 |

| 3 | DEBUG UART | Debug serial port | PH1.25 female header(4 Pin) | P14 |

| 4 | RS232 | RS232 interface | screw terminals | P15 |

| 5 | RS485 | RS485 interface | screw terminals | P16和P18 |

| 6 | CAN | CAN interface | screw terminals | P21 |

| 7 | 4G module | 4G module interface | MINI-PCIE | P19 |

| 8 | sim | sim card | MICRO SIM self-propelled | P27 |

| 9 | TF | TF card | Standard TF card self-elastic deck | P13 |

| 10 | USB | USB2.0 | Double layer USB_A | P9 |

| 11 | HDMI | video interface | Standard HDMI-A port | P7 |

| 12 | MIPI-DSI | MIPI DSI screen interface | FPC socket(40 Pin) | P23 |

| 13 | LVDS | LVDS screen interface | FPC socket(40 Pin) | P24 |

| 14 | RGB | RGB screen interface | FPC socket(40 Pin) | P25 |

| 15 | USER LIGHT | User LED light | SMD LED lights (3 pcs) | D3、D5、D6 |

| 16 | Antenna | WIFI & Bluetooth | IPX Connector | E1 |

| 17 | USB | BOOT | LOADER Micro_USB | P8 |

| 18 | Audio | Audio output, input | 3.5mm headphone holder | P4 |

| 19 | Reset button | reset | touch key switch | SW6 |

| 20 | Download button | Download | touch key switch | SW8 |

| 21 | Custom button | KEYADC button | touch key switch | SW1~SW5 |

| 22 | SATA | SATA interface | SATA 7P interface | P6 |

| 23 | MIPI-CSI | Parallel camera interface | Double row PH2.54(20 Pin) | P2 |

A40I Bottom Plate Description

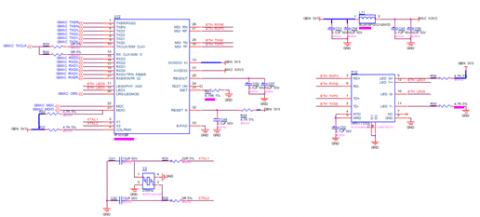

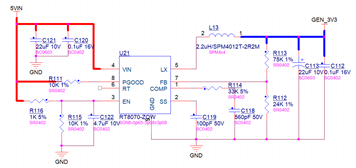

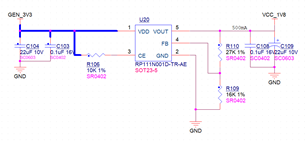

Bottom plate Power

The bottom plate uses the DC 5.5 plug (P22) socket to insert the 5V power supply for power supply, through (P26) mechanical power switch, self-recovery fuse (F1), (D8) 5.6V Zener diode and Q7 transistor through the power input feedback detection and control of 5VDC-DC ( Q6) pin4 EN pin high and low level input, control power on and off to prevent power input overvoltage protection. The output 5VIN voltage of the latter stage is filtered by capacitors and magnetic beads and then stepped down by 3.3V and 1.8V in turn to supply power to some circuits of the control base plate.

Note: When designing the power supply part, please follow the minimum 3A current for 5V/3.3V copper cladding and power wiring. If you need to route the front and back, you need to drill more holes to prevent the power supply from being overloaded and cause the PCB to burn the board and ensure the power supply is normal.

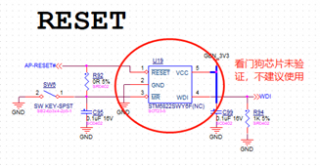

Reset circuit

Note: This development board only uses the SW6 reset switch in the picture, and the door dog chip has not been verified, so it is not recommended to use it.

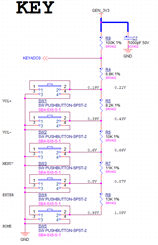

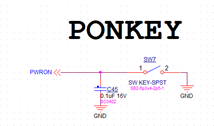

Button circuit

VOL+, VOL-, MENU, ENTER, HOME buttons input 3.3V through KEYADC0 to pull up different resistors to ground, and do level recognition to distinguish function buttons; DOWNLOAD, PWRON are separate buttons, and it is effective to directly press the button to ground.

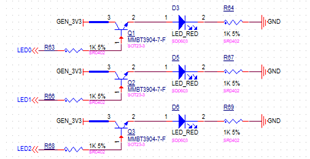

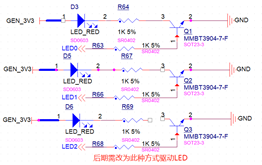

LED display

Note:This system is equipped with 3-channel LED output display. It is recommended that the pull-up input power supply should be changed from 3.3V to 5V input in the later stage, and the driving method should be changed to the circuit shown in the figure below to prevent the LED with higher driving voltage from being insufficiently bright.

RTC real-time clock circuit

The RTC chip used in this circuit has a built-in crystal oscillator matching capacitor. If you need to replace the solution, you need to pay attention to the crystal oscillator accuracy. You can connect the matching capacitor to the ground in parallel on the two crystal oscillator networks to meet the needs of adjustment accuracy. When the backplane is powered on, the 3.3V power supply of the backplane will supply power to the RTC chip and charge the battery BT1; when the backplane is powered off, the battery BT1 will discharge and serve as the power supply for the RTC chip to work.

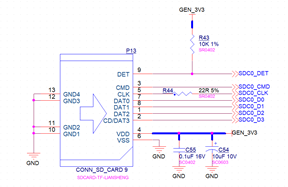

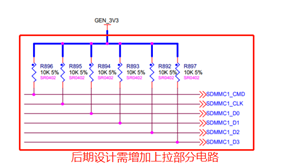

External TF card circuit

Note:The SDIO interface network on the right side of the figure is connected to the pull-up resistor. When designing the PCB, it is necessary to do equal-length processing and require 3W spacing and do overall package processing. In subsequent design and development, please connect pull-up resistors to all 7 SDCO signal lines.

Ethernet circuit interface

Note:It is required that the ETH TX/RX signal line PCB design needs to be equal-length processing and requires 3W spacing and overall grounding processing. The differential pair and other networks must maintain a spacing of more than 3 times the line width; the differential pair requires the equal-length error range to be within 5mil Within the differential pair, the equal-length error range is required to be within 25mil, and the power supply part needs to thicken the filter capacitor as close to the terminal as possible.

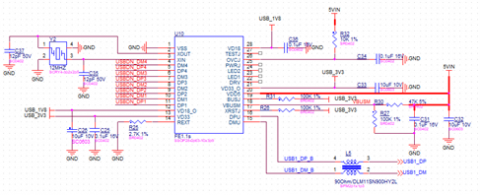

USB circuit

Note:The 5VIN power supply needs to strictly reserve at least 1.5A through the current design to be bold, and the DP/DM signal line needs to go through the differential signal line. BR2/3 are anti-static protection devices, L5/6/8 are common-mode filters, and need to be close to the USB interface when designing the PCB. P9 is a USB2.0 socket that can be connected to a USB flash drive or a mouse.

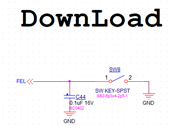

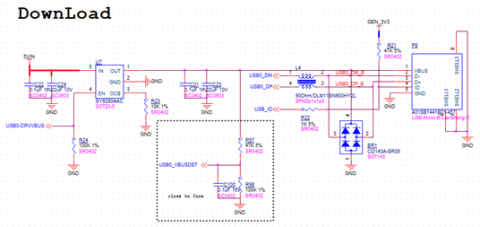

DownLoad burns the system USB port circuit

This interface is a Micro USB interface, which is used to connect the host PC to the development board to program the system. In the figure, the ID pin of the USB interface needs to be pulled up and cannot be connected to a low level; BR1 is to protect the device against static electricity, and L4 is a common mode filter, which needs to be close to the Micro USB interface when designing the PCB; the USB cable requires differential equal-length traces.

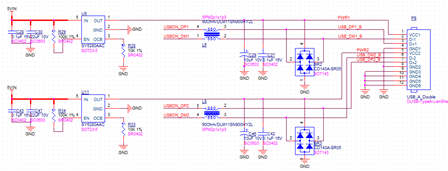

4G module circuit

Note:The instantaneous working current of the 4G module can reach about 3A. When designing the circuit, the 3.3v power line should be designed strictly according to the current, and the filter capacitor should be placed as close as possible; D4 is the working status indicator of the module, and P27S is the SIM card holder, which needs to be placed close to the 4G module. , the module to the SIM card network requires grouped wiring to avoid the wiring being too far, the length error is too large, and it is far away from the strong signal interference source and the wiring needs to be arranged nearby. L12 is a common mode filter, and the USB cable requires differential routing.

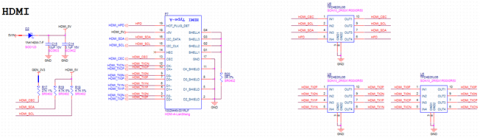

HDMI display circuit

Note:U4/5/6 are TVS electrostatic protection tubes. When designing the PCB, place them as close to the HDMI socket as possible. Except for the power cable, the remaining signal lines need to be routed according to the differential rules and have the same length in the differential pair. The differential pair and other networks should be kept three times as long. For the spacing above the line width, the equal length error range within the differential pair is required to be within 5 mil, and the equal length error range between the differential pair is required to be within 15 mil. HDMI_CEC / HDMI_SDA/ HDMI_SCL need to be pulled up strictly according to the circuit diagram.

RGB/LVDS/DSI circuits

Note:The 5V/3.3V power supply needs to be designed according to the current above 1A. Except for the power line, the rest of the signal lines must be wired in strict accordance with the equidistant differential signal lines.

WIFI &Bluetooth module circuit

Note: The 3.3V power supply should be designed according to the current above 1.5A, the signal line circuit should be pulled up strictly according to the schematic diagram, the SDIO network group should be wired with equal length, the output line of the chip pin1 WL_BT_ANY output signal terminal should be widened as much as possible, and the network where E1 is located requires the wiring to meet 50Ω Impedance design, the traces should be as short as possible and no corners should be taken. Devices such as C93/R73/C92 should be as close as possible to the π-type output, and both ends of the antenna output should be covered with copper GND as much as possible.

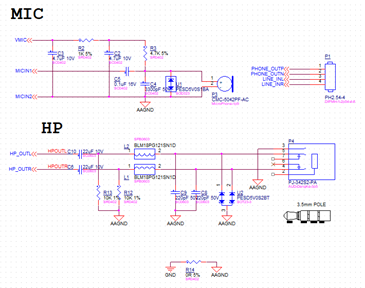

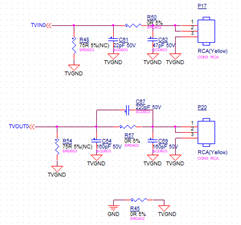

MIC/HP/TVIN/TVOUT circuit

Note:The MIC and HP traces need to be hollowed out without copper traces. The two groups of AAGND and TVGND need to be connected in series with resistors to isolate them from GND. The traces of analog signals such as microphones and headphones should be thickened to more than 10 mils, and the traces should be smooth.

RS232/485/CAN circuit

Note: The 3.3V power supply needs to be designed according to the current above 1A, and the TX/RX signal line circuit needs to be wired strictly according to the equidistant differential signal line. P14 is the internal debugging port. For the convenience of later debugging, please lead out this debugging serial port when designing the backplane by yourself. The matching resistor R47/R52 of the 485 signal terminal is increased by 120 ohms depending on the number of loads and the transmission length. When the device is laid out, the U16 and U17 chips are placed close to the P21 interface.

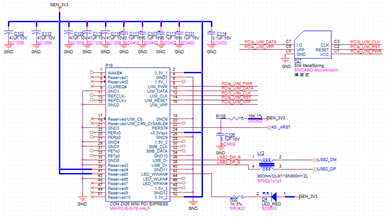

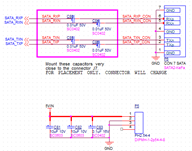

SATA interface circuit

Note:When designing the PCB, the two signal lines of each IIC should be routed in groups to avoid too much error in the length of the two network lines in the group when the lines are too far.。

CSI (DVP) interface circuit

The P2 port leads out the reserved IO for the core board, and the output signal line needs to be as short as possible in groups and differentially long traces. The 3.3V/1.8V circuit current needs to be designed at more than 500mA.

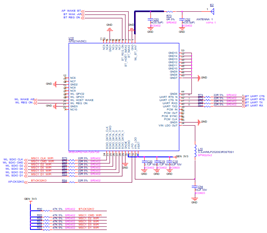

IIC parallel and core board connection circuit

A single IIC bus can mount multiple devices, and 0 ohm resistors are reserved for debugging. Each IIC bus should be connected to a pull-up resistor to the logic level so that the signal line does not float and the drive capability is enhanced. When designing the PCB, the two signal lines of each IIC should be traced in groups, so as to avoid the error of the length of the two network traces in the group when the traces are too far.

Core board power supply part of the 5V power supply needs to reserve 3A current copper and power trace, if you need to trace the front and back sides of the wire need to punch more holes, to prevent the power supply instantaneous overload caused by PCB burning board, to ensure normal power supply. The filter capacitor should be placed nearby, and the output signal line should be shortened as much as possible in groups and differentially long traces.