“MYZR-RZG2UL-CB200”的版本间的差异

来自明远智睿的wiki

(→尺寸) |

|||

| (未显示同一用户的1个中间版本) | |||

| 第27行: | 第27行: | ||

|32G | |32G | ||

|} | |} | ||

| + | == '''硬件接口''' == | ||

| + | |||

| + | <table border-collapse="collapse" border="2" cellspacing="10" style="width:700px" align="left" rules="none" cellspacing="8" rules="all"> | ||

| + | <tr align="center"><th colspan="2" >接口规格</th><th >最大可配置接口数</th><th >描述 </th></tr> | ||

| + | <tr align="center"><td rowspan="5" >CPU</td> <td >框架 </td> <td > 2 </td> <td >1.0 GHzSingleCortex-A55 r2p0(Armv8-A) core,Cortex-M33 r0p4(ARMv8-M) </td> </tr> | ||

| + | <tr align="center"> <td >处理器 </td> <td > 1 </td> <td >Renesas RZ/G2UL </td> </tr> | ||

| + | <tr align="center"> <td >主频 </td> <td > 1 </td> <td >1.0GHz </td> </tr> | ||

| + | <tr align="center"> <td >位宽 </td> <td > 1 </td> <td >64 bit </td> </tr> | ||

| + | <tr align="center"> <td >视频硬件加速(VPU) </td> <td > 1 </td> <td >ISU </td> </tr> | ||

| + | <tr align="center"><td rowspan="2" >内存</td> <td >eMMC </td> <td > 1 </td> <td >8G扩展至64GB </td></tr> | ||

| + | <tr align="center"> <td >DDR </td> <td > 1 </td> <td >1/2GB </td> </tr> | ||

| + | <tr align="center"><td rowspan="11" >接口</td><td >Ethernet </td> <td > 2 </td> <td >10/100/1000Mbit/s </td> </tr> | ||

| + | <tr align="center"> <td >USB </td> <td > 2 </td> <td >(1xHost+1xOTG) </td> </tr> | ||

| + | <tr align="center"> <td >UART </td> <td > 5 </td> <td >支持 5bit,6bit,7bit,8bit 串行数据收发 </td> </tr> | ||

| + | <tr align="center"> <td >CAN </td> <td > 2 </td> <td >2路CAN2.0,最高速率1Mb/sec </td> </tr> | ||

| + | <tr align="center"> <td >lIC </td> <td > 4 </td> <td >4路12C最高支持400 kbps </td> </tr> | ||

| + | <tr align="center"> <td >SPI </td> <td > 3 </td> <td >支持串行主/从模式,最大传输速率33 Mbps </td> </tr> | ||

| + | <tr align="center"> <td >MMC/SD/SDIO </td> <td > 1 </td> <td >4bit,符合eMMC 4.51 </td> </tr> | ||

| + | <tr align="center"> <td >SSI </td> <td > 4 </td> <td >支持I2S/单声道/TDM音频格式 </td> </tr> | ||

| + | <tr align="center"> <td >CSI </td> <td > 1 </td> <td >支持1/2/4 lane,每lane最高支持1.5 Gbps </td> </tr> | ||

| + | <tr align="center"> <td >RGB </td> <td > 1 </td> <td >支持最大分辨率1280×800 60Hz, 格式为RGB666/RGB888 </td> </tr> | ||

| + | <tr align="center"> <td >ADC </td> <td > 2 </td> <td >12bit精度 </td> </tr> | ||

| + | <tr align="center"><td rowspan="4" >通用规格</td> <td >工作电压 </td> <td > 1 </td> <td >3.6V </td></tr> | ||

| + | <tr align="center"> <td >工作温度 </td> <td > 1 </td> <td >-40°C to +85°C </td> </tr> | ||

| + | <tr align="center"> <td >待机功耗 </td> <td > 1 </td> <td >0.6W </td> </tr> | ||

| + | <tr align="center"> <td >尺寸 </td> <td > 1 </td> <td > 67.6mm x26.1 mm </td> </tr> | ||

| + | <tr align="center"><td rowspan="2" >software</td> <td >内核版本 </td> <td > 1 </td> <td >Linux 5.10 </td></tr> | ||

| + | <tr align="center"> <td >图形界面 </td> <td > 1 </td> <td >QT5 </td> </tr> | ||

| + | </table><br/><br/><br/> | ||

| + | <br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/><br/> | ||

| + | |||

| + | |||

| + | |||

== '''供电电源''' == | == '''供电电源''' == | ||

5V输入<br> | 5V输入<br> | ||

2023年4月18日 (二) 10:01的最新版本

目录

MYZR-RZG2UL-CB200 视图

核心板MYZR-RZG2UL-CB200 正面

核心板MYZR-RZG2UL-CB200 背面

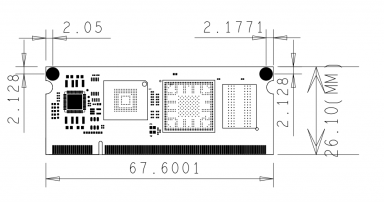

尺寸

MYZR-RZG2UL-CB200参数

硬件配置

| CPU |

双核 Cortex-A55 |

主频 1.2Ghz |

|---|---|---|

| 内存 | 单通道 16bit DDR4 |

2G |

| 存储 | eMMC |

32G |

硬件接口

| 接口规格 | 最大可配置接口数 | 描述 | |

|---|---|---|---|

| CPU | 框架 | 2 | 1.0 GHzSingleCortex-A55 r2p0(Armv8-A) core,Cortex-M33 r0p4(ARMv8-M) |

| 处理器 | 1 | Renesas RZ/G2UL | |

| 主频 | 1 | 1.0GHz | |

| 位宽 | 1 | 64 bit | |

| 视频硬件加速(VPU) | 1 | ISU | |

| 内存 | eMMC | 1 | 8G扩展至64GB |

| DDR | 1 | 1/2GB | |

| 接口 | Ethernet | 2 | 10/100/1000Mbit/s |

| USB | 2 | (1xHost+1xOTG) | |

| UART | 5 | 支持 5bit,6bit,7bit,8bit 串行数据收发 | |

| CAN | 2 | 2路CAN2.0,最高速率1Mb/sec | |

| lIC | 4 | 4路12C最高支持400 kbps | |

| SPI | 3 | 支持串行主/从模式,最大传输速率33 Mbps | |

| MMC/SD/SDIO | 1 | 4bit,符合eMMC 4.51 | |

| SSI | 4 | 支持I2S/单声道/TDM音频格式 | |

| CSI | 1 | 支持1/2/4 lane,每lane最高支持1.5 Gbps | |

| RGB | 1 | 支持最大分辨率1280×800 60Hz, 格式为RGB666/RGB888 | |

| ADC | 2 | 12bit精度 | |

| 通用规格 | 工作电压 | 1 | 3.6V |

| 工作温度 | 1 | -40°C to +85°C | |

| 待机功耗 | 1 | 0.6W | |

| 尺寸 | 1 | 67.6mm x26.1 mm | |

| software | 内核版本 | 1 | Linux 5.10 |

| 图形界面 | 1 | QT5 | |

供电电源

5V输入

温度范围

工作温度

- 商业级:

- 0°C ~ 70°C

- 0°C ~ 70°C

- 工业级:

- -40°C ~ 85°C

- -40°C ~ 85°C

存储温度

- -60°C ~ 125°C

- -60°C ~ 125°C

操作系统支持

- Linux

Linux-5.10.131

管脚定义&详细功能说明(LCD版本)

| Pin NO. | Pin Name | Power | Function | 描述 |

| 2 | GND | 0V | 地 | |

| 4 | GND | 0V | 地 | |

| 6 | GND | 0V | 地 | |

| 8 | GND | 0V | 地 | |

| 10 | GND | 0V | 地 | |

| 12 | ||||

| 14 | ||||

| 16 | ||||

| 18 | PMIC_I2C_SCL | 3.3V | — | — |

| 20 | PMIC_I2C_SDA | 3.3V | — | — |

| 22 | ||||

| 24 | RZ_QSPI0_WP# | 3.3V | QSPI_WP# | — |

| 26 | RZ_QSPI0_SSL | 3.3V | QSPI0_SSL | 内部上拉 |

| 28 | RZ_QSPI0_IO1 | 3.3V | QSPI0_IO1 | — |

| 30 | RZ_QSPI0_SPCLK | 3.3V | QSPI0_SPCLK | 内部上拉 |

| 32 | RZ_QSPI_RESET# | 3.3V | QSPI_RESET# | 内部上拉 |

| 34 | RZ_QSPI0_IO2 | 3.3V | QSPI0_IO2 | — |

| 36 | RZ_QSPI0_IO0 | 3.3V | QSPI0_IO0 | — |

| 38 | RZ_QSPI0_IO3 | 3.3V | QSPI0_IO3 | |

| 40 | ||||

| 42 | ||||

| 44 | RZ_MD_BOOT1 | 3.3V | MD_BOOT1 | |

| 46 | RZ_MD_BOOT2 | 3.3V | MD_BOOT2 | |

| 48 | RZ_MD_BOOT0 | 3.3V | MD_BOOT0 | — |

| 50 | RZ_AUDIO_CLK1 | 3.3V | AUDIO_CLK1 | — |

| 52 | RZ_AUDIO_CLK2 | 3.3V | AUDIO_CLK2 | — |

| 54 | ||||

| 56 | RZ_OM_DQS | 3.3V | OM_DQS | — |

| 58 | RZ_OM_SIO4 | 3.3V | OM_SIO4 | — |

| 60 | RZ_OM_SIO5 | 3.3V | OM_SIO5 | — |

| 62 | RZ_OM_SIO6 | 0V | OM_SIO6 | — |

| 64 | RZ_OM_SIO7 | 3.3V | OM_SIO7 | — |

| 66 | RZ_OM_CS1_N | 3.3V | OM_CS1_N | 内部上拉 |

| 68 | ||||

| 70 | RZ_SD1_CLK | 3.3V | SD1_CLK | — |

| 72 | RZ_SD1_D2 | 3.3V | SD1_DATA2 | 内部上拉 |

| 74 | RZ_SD1_D0 | 3.3V | SD1_DATA0 | 内部上拉 |

| 76 | RZ_SD1_D1 | 3.3V | SD1_DATA1 | 内部上拉 |

| 78 | RZ_SD1_D3 | 3.3V | SD1_DATA3 | 内部上拉 |

| 80 | RZ_SD1_CMD | 3.3V | SD1_CMD | 内部上拉 |

| 82 | RZ_IRQ1 | 3.3V | P0_3/SD1_WP/MTIOC1B/RIIC2_SCL/IRQ1 | — |

| 84 | RZ_SD1_CD# | 3.3V | P0_2/SD1_CD/MTIOC1A/RIIC2_SDA/IRQ0 | 内部上拉 |

| 86 | ||||

| 88 | RZ_MTIOC2A_PWM | 3.3V | P0_0/SD0_CD/RIIC3_SDA/MTIOC2A/SCI0_TXD | — |

| 90 | RZ_MTIOC2B_PWM | 3.3V | P0_1/SD0_WP/RIIC3_SCL/MTIOC2B/SCI0_RXD | — |

| 92 | ||||

| 94 | ||||

| 96 | RZ_SCIF0_RXD | 3.3V | P6_3/RIIC2_SDA/RSPI2_SSL/CAN0_TX_DATARATE_EN/SCIF2_CTS#/MTIOC7D/SCIF0_RXD/IRQ3 | — |

| 98 | RZ_SCIF0_TXD | 3.3V | P6_4/RIIC2_SCL/CAN0_RX_DATARATE_EN/SCIF2_RTS#/ADC_TRG/SCIF0_TXD/IRQ4 | — |

| 100 | GPIO6_2 | 3.3V | P6_2/ADC_TRG/RSPI2_MISO/CAN0_RX/SCIF2_SCK/MTIOC7C/IRQ2 | — |

| 102 | RZ_USB1_OVRCUR | 3.3V | P6_1/USB1_OVRCUR/RSPI2_MOSI/CAN0_TX/SCIF2_RXD/MTIOC7B | — |

| 104 | RZ_USB1_VBUSEN | 3.3V | P6_0/USB1_VBUSEN/RSPI2_CK/CAN_CLK/SCIF2_TXD/MTIOC7A | — |

| 106 | RZ_MTIPC7C_PWM | 3.3V | P5_2/USB0_OVRCUR/SCIF2_SCK/MTIOC7C/SSI2_BCK | — |

| 108 | RZ_SCIF2_TXD | 3.3V | P5_0/USB0_VBUSEN/SCIF2_TXD/MTIOC7A | — |

| 110 | RZ_SCIF2_RXD | 3.3V | P5_1/SCIF2_RXD/MTIOC7B/ADC_TRG/SCI0_CTS#/RTS#/RSPI0_SSL/IRQ2 | — |

| 112 | ||||

| 114 | ||||

| 116 | ||||

| 118 | ||||

| 120 | ||||

| 122 | ||||

| 124 | ||||

| 126 | ||||

| 128 | ||||

| 130 | ||||

| 132 | ||||

| 134 | ||||

| 136 | ||||

| 138 | ||||

| 140 | RZ_DISP_DATA13 | 3.3V | P15_1/RSPI0_MOSI/IRQ5/MTIOC8B/DISP_DATA13 | Pixel data Green5 |

| 142 | RZ_DISP_DATA11 | 3.3V | P15_0/RSPI0_CK/IRQ4/MTIOC8A/DISP_DATA11 | Pixel data Green3 |

| 144 | RZ_DISP_DATA14 | 3.3V | P15_3/RSPI0_SSL/IRQ7/MTIOC8D/DISP_DATA14 | Pixel data Green6 |

| 146 | RZ_DISP_DATA16 | 3.3V | P15_2/RSPI0_MISO/IRQ6/MTIOC8C/DISP_DATA16/SCI1_TXD | Pixel data Blue0 |

| 148 | RZ_DISP_DATA22 | 3.3V | P17_3/RSPI1_SSL/SSI1_RXD/CAN1_RX_DATARATE_EN/MTIOC3D/DISP_DATA22 | Pixel data Blue6 |

| 150 | RZ_DISP_DATA17 | 3.3V | P17_0/RSPI1_CK/SSI1_BCK/CAN1_TX/MTIOC3A/DISP_DATA17/SCI1_RXD | Pixel data Blue1 |

| 152 | RZ_DISP_DATA18 | 3.3V | P17_2/RSPI1_MISO/SSI1_TXD/CAN1_TX_DATARATE_EN/MTIOC3C/DISP_DATA18 | Pixel data Blue2 |

| 154 | RZ_DISP_DATA19 | 3.3V | P17_1/RSPI1_MOSI/SSI1_RCK/CAN1_RX/MTIOC3B/DISP_DATA19 | Pixel data Blue3 |

| 156 | RZ_DISP_DATA7 | 3.3V | P14_0/SCIF1_TXD/CAN1_TX/MTIC5U/SCI0_RXD/DISP_DATA7 | Pixel data Red7 |

| 158 | RZ_DISP_DATA9 | 3.3V | P14_1/SCIF1_RXD/CAN1_RX/MTIC5V/SCI0_TXD/DISP_DATA9/IRQ2 | Pixel data Green1 |

| 160 | RZ_DISP_DATA10 | 3.3V | P16_0/SCIF1_CTS#/CAN1_RX_DATARATE_EN/SCI0_CTS#/RTS#/DISP_DATA10 | Pixel data Green2/初始状态不可为高 |

| 162 | RZ_DISP_DATA12 | 3.3V | P16_1/SCIF1_RTS#/DISP_DATA12 | Pixel data Green4/初始状态不可为高 |

| 164 | RZ_DISP_DATA0 | 3.3V | P11_2/SSI0_TXD/POE8#/SCI1_SCK/RSPI2_MISO/DISP_DATA0/SCIF1_TXD | Pixel data Red0 |

| 166 | RZ_DISP_DATA1 | 3.3V | P13_1/SCIF0_RXD/CAN0_TX/MTIOC4B/USB1_OVRCUR/DISP_DATA1/SCIF1_RXD | Pixel data Red1 |

| 168 | RZ_DISP_DATA5 | 3.3V | P12_1/IRQ1/SCI0_TXD/MTIOC0B/SCIF3_RXD/DISP_DATA5 | Pixel data Red5 |

| 170 | RZ_DISP_VSYNC | 3.3V | P12_0/IRQ0/SCI0_RXD/MTIOC0A/SCIF3_TXD/DISP_VSYNC | Vertical sync pulse |

| 172 | RZ_DISP_HSYNC | 3.3V | P11_0/SSI0_BCK/POE0#/SCI1_RXD/RSPI2_CK/DISP_HSYNC | Horizontal sync pulse |

| 174 | GND | 0V | 地 | |

| 176 | RZ_DISP_CLK | 3.3V | P11_3/SSI0_RXD/POE10#/SCI1_CTS#/RTS#/RSPI2_SSL/DISP_CLK | Pixel clock |

| 178 | GND | 0V | 地 | |

| 180 | RZ_DISP_DATA2 | 3.3V | P13_0/SCIF0_TXD/CAN_CLK/MTIOC4A/USB1_VBUSEN/DISP_DATA2 | Pixel data Red2 |

| 182 | RZ_DISP_DATA4 | 3.3V | P13_3/SCIF0_CTS#/CAN0_TX_DATARATE_EN/MTIOC4D/DISP_DATA4 | Pixel data Red4 |

| 184 | RZ_DISP_DATA8 | 3.3V | P14_2/SCIF1_SCK/ADC_TRG/CAN1_TX_DATARATE_EN/MTIC5W/SCI0_SCK/DISP_DATA8/IRQ3 | Pixel data Green0 |

| 186 | RZ_DISP_DATA6 | 3.3V | P13_2/SCIF0_SCK/CAN0_RX/MTIOC4C/DISP_DATA6 | Pixel data Red6 |

| 188 | RZ_DISP_DE | 3.3V | P11_1/SSI0_RCK/POE4#/SCI1_TXD/RSPI2_MOSI/DISP_DE | Enable |

| 190 | RZ_DISP_DATA3 | 3.3V | P13_4/SCIF0_RTS#/CAN0_RX_DATARATE_EN/DISP_DATA3 | Pixel data Red3 |

| 192 | RZ_DISP_DATA23 | 3.3V | P18_3/IRQ5/RSPI0_MOSI/SCI0_TXD/SCIF3_TXD/SCI0_CTS#/RTS#/DISP_DATA23/SCIF4_SCK | Pixel data Blue7 |

| 194 | RZ_DISP_DATA15 | 3.3V | P18_0/IRQ2/ADC_TRG/SCI0_SCK/DISP_DATA15/SCIF3_SCK | Pixel data Green7 |

| 196 | RZ_DISP_DATA20 | 3.3V | P18_1/IRQ3/SCIF3_SCK/SCI0_TXD/DISP_DATA20/SCIF3_RXD | Pixel data Blue4 |

| 198 | RZ_DISP_DATA21 | 3.3V | P18_2/IRQ4/RSPI0_CK/SCI0_SCK/SCIF3_RXD/SCI0_RXD/DISP_DATA21/SCIF3_TXD | Pixel data Blue5 |

| 200 |

管脚定义&详细功能说明(ETH版本)

| Pin NO. | Pin Name | Power | Function | 描述 |

| 2 | GND | 0V | 地 | |

| 4 | GND | 0V | 地 | |

| 6 | GND | 0V | 地 | |

| 8 | GND | 0V | 地 | |

| 10 | GND | 0V | 地 | |

| 12 | ||||

| 14 | ||||

| 16 | ||||

| 18 | PMIC_I2C_SCL | 3.3V | — | — |

| 20 | PMIC_I2C_SDA | 3.3V | — | — |

| 22 | ||||

| 24 | RZ_QSPI0_WP# | 3.3V | QSPI_WP# | — |

| 26 | RZ_QSPI0_SSL | 3.3V | QSPI0_SSL | 内部上拉 |

| 28 | RZ_QSPI0_IO1 | 3.3V | QSPI0_IO1 | — |

| 30 | RZ_QSPI0_SPCLK | 3.3V | QSPI0_SPCLK | 内部上拉 |

| 32 | RZ_QSPI_RESET# | 3.3V | QSPI_RESET# | 内部上拉 |

| 34 | RZ_QSPI0_IO2 | 3.3V | QSPI0_IO2 | — |

| 36 | RZ_QSPI0_IO0 | 3.3V | QSPI0_IO0 | — |

| 38 | RZ_QSPI0_IO3 | 3.3V | QSPI0_IO3 | |

| 40 | ||||

| 42 | ||||

| 44 | RZ_MD_BOOT1 | 3.3V | MD_BOOT1 | |

| 46 | RZ_MD_BOOT2 | 3.3V | MD_BOOT2 | |

| 48 | RZ_MD_BOOT0 | 3.3V | MD_BOOT0 | — |

| 50 | RZ_AUDIO_CLK1 | 3.3V | AUDIO_CLK1 | — |

| 52 | RZ_AUDIO_CLK2 | 3.3V | AUDIO_CLK2 | — |

| 54 | ||||

| 56 | RZ_OM_DQS | 3.3V | OM_DQS | — |

| 58 | RZ_OM_SIO4 | 3.3V | OM_SIO4 | — |

| 60 | RZ_OM_SIO5 | 3.3V | OM_SIO5 | — |

| 62 | RZ_OM_SIO6 | 0V | OM_SIO6 | — |

| 64 | RZ_OM_SIO7 | 3.3V | OM_SIO7 | — |

| 66 | RZ_OM_CS1_N | 3.3V | OM_CS1_N | 内部上拉 |

| 68 | ||||

| 70 | RZ_SD1_CLK | 3.3V | SD1_CLK | — |

| 72 | RZ_SD1_D2 | 3.3V | SD1_DATA2 | 内部上拉 |

| 74 | RZ_SD1_D0 | 3.3V | SD1_DATA0 | 内部上拉 |

| 76 | RZ_SD1_D1 | 3.3V | SD1_DATA1 | 内部上拉 |

| 78 | RZ_SD1_D3 | 3.3V | SD1_DATA3 | 内部上拉 |

| 80 | RZ_SD1_CMD | 3.3V | SD1_CMD | 内部上拉 |

| 82 | SD1_WP# | 3.3V | P0_3/SD1_WP/MTIOC1B/RIIC2_SCL/IRQ1 | — |

| 84 | RZ_SD1_CD# | 3.3V | P0_2/SD1_CD/MTIOC1A/RIIC2_SDA/IRQ0 | 内部上拉 |

| 86 | ||||

| 88 | RZ_MTIOC2A_PWM | 3.3V | P0_0/SD0_CD/RIIC3_SDA/MTIOC2A/SCI0_TXD | — |

| 90 | RZ_MTIOC2B_PWM | 3.3V | P0_1/SD0_WP/RIIC3_SCL/MTIOC2B/SCI0_RXD | — |

| 92 | ||||

| 94 | ||||

| 96 | RZ_SCIF0_RXD | 3.3V | P6_3/RIIC2_SDA/RSPI2_SSL/CAN0_TX_DATARATE_EN/SCIF2_CTS#/MTIOC7D/SCIF0_RXD/IRQ3 | — |

| 98 | RZ_SCIF0_TXD | 3.3V | P6_4/RIIC2_SCL/CAN0_RX_DATARATE_EN/SCIF2_RTS#/ADC_TRG/SCIF0_TXD/IRQ4 | — |

| 100 | CAN0_RX_D | 3.3V | P6_2/ADC_TRG/RSPI2_MISO/CAN0_RX/SCIF2_SCK/MTIOC7C/IRQ2 | — |

| 102 | CAN0_TX_D | 3.3V | P6_1/USB1_OVRCUR/RSPI2_MOSI/CAN0_TX/SCIF2_RXD/MTIOC7B | — |

| 104 | GPIO6_0 | 3.3V | P6_0/USB1_VBUSEN/RSPI2_CK/CAN_CLK/SCIF2_TXD/MTIOC7A | — |

| 106 | RZ_MTIPC7C_PWM | 3.3V | P5_2/USB0_OVRCUR/SCIF2_SCK/MTIOC7C/SSI2_BCK | — |

| 108 | RZ_SCIF2_TXD | 3.3V | P5_0/USB0_VBUSEN/SCIF2_TXD/MTIOC7A | — |

| 110 | RZ_SCIF2_RXD | 3.3V | P5_1/SCIF2_RXD/MTIOC7B/ADC_TRG/SCI0_CTS#/RTS#/RSPI0_SSL/IRQ2 | — |

| 112 | ||||

| 114 | ||||

| 116 | ||||

| 118 | ||||

| 120 | ||||

| 122 | ||||

| 124 | ||||

| 126 | ||||

| 128 | ||||

| 130 | ||||

| 132 | ||||

| 134 | ||||

| 136 | ||||

| 138 | ||||

| 140 | RSPI0_MOSI_B | 3.3V | P15_1/RSPI0_MOSI/IRQ5/MTIOC8B/DISP_DATA13 | — |

| 142 | RSPI0_CK_B | 3.3V | P15_0/RSPI0_CK/IRQ4/MTIOC8A/DISP_DATA11 | — |

| 144 | RSPI0_SSL_B | 3.3V | P15_3/RSPI0_SSL/IRQ7/MTIOC8D/DISP_DATA14 | — |

| 146 | RSPI0_MISO_B | 3.3V | P15_2/RSPI0_MISO/IRQ6/MTIOC8C/DISP_DATA16/SCI1_TXD | — |

| 148 | SSI1_RXD_C | 3.3V | P17_3/RSPI1_SSL/SSI1_RXD/CAN1_RX_DATARATE_EN/MTIOC3D/DISP_DATA22 | — |

| 150 | SSI1_BCK_C | 3.3V | P17_0/RSPI1_CK/SSI1_BCK/CAN1_TX/MTIOC3A/DISP_DATA17/SCI1_RXD | — |

| 152 | SSI1_TXD_C | 3.3V | P17_2/RSPI1_MISO/SSI1_TXD/CAN1_TX_DATARATE_EN/MTIOC3C/DISP_DATA18 | — |

| 154 | SSI1_RCK_C | 3.3V | P17_1/RSPI1_MOSI/SSI1_RCK/CAN1_RX/MTIOC3B/DISP_DATA19 | — |

| 156 | CAN1_TX_C | 3.3V | P14_0/SCIF1_TXD/CAN1_TX/MTIC5U/SCI0_RXD/DISP_DATA7 | — |

| 158 | CAN1_RX_C | 3.3V | P14_1/SCIF1_RXD/CAN1_RX/MTIC5V/SCI0_TXD/DISP_DATA9/IRQ2 | — |

| 160 | SCIF1_CTS# | 3.3V | P16_0/SCIF1_CTS#/CAN1_RX_DATARATE_EN/SCI0_CTS#/RTS#/DISP_DATA10 | 初始状态不可为高 |

| 162 | SCIF1_RTS# | 3.3V | P16_1/SCIF1_RTS#/DISP_DATA12 | 初始状态不可为高 |

| 164 | SCIF1_TXD_C | 3.3V | P11_2/SSI0_TXD/POE8#/SCI1_SCK/RSPI2_MISO/DISP_DATA0/SCIF1_TXD | — |

| 166 | SCIF1_RXD_C | 3.3V | P13_1/SCIF0_RXD/CAN0_TX/MTIOC4B/USB1_OVRCUR/DISP_DATA1/SCIF1_RXD | — |

| 168 | SCIF3_RXD | 3.3V | P12_1/IRQ1/SCI0_TXD/MTIOC0B/SCIF3_RXD/DISP_DATA5 | — |

| 170 | SCIF3_TXD | 3.3V | P12_0/IRQ0/SCI0_RXD/MTIOC0A/SCIF3_TXD/DISP_VSYNC | — |

| 172 | GPIO11_0 | 3.3V | P11_0/SSI0_BCK/POE0#/SCI1_RXD/RSPI2_CK/DISP_HSYNC | — |

| 174 | GND | 0V | 地 | |

| 176 | GPIO11_3 | 3.3V | P11_3/SSI0_RXD/POE10#/SCI1_CTS#/RTS#/RSPI2_SSL/DISP_CLK | — |

| 178 | GND | 0V | 地 | |

| 180 | GPIO13_0 | 3.3V | P13_0/SCIF0_TXD/CAN_CLK/MTIOC4A/USB1_VBUSEN/DISP_DATA2 | — |

| 182 | MTIOC4D | 3.3V | P13_3/SCIF0_CTS#/CAN0_TX_DATARATE_EN/MTIOC4D/DISP_DATA4 | — |

| 184 | ADC_TRG | 3.3V | P14_2/SCIF1_SCK/ADC_TRG/CAN1_TX_DATARATE_EN/MTIC5W/SCI0_SCK/DISP_DATA8/IRQ3 | — |

| 186 | GPIO13_2 | 3.3V | P13_2/SCIF0_SCK/CAN0_RX/MTIOC4C/DISP_DATA6 | — |

| 188 | GPIO11_1 | 3.3V | P11_1/SSI0_RCK/POE4#/SCI1_TXD/RSPI2_MOSI/DISP_DE | — |

| 190 | GPIO13_4 | 3.3V | P13_4/SCIF0_RTS#/CAN0_RX_DATARATE_EN/DISP_DATA3 | — |

| 192 | IRQ5_A | 3.3V | P18_3/IRQ5/RSPI0_MOSI/SCI0_TXD/SCIF3_TXD/SCI0_CTS#/RTS#/DISP_DATA23/SCIF4_SCK | — |

| 194 | IRQ2_A | 3.3V | P18_0/IRQ2/ADC_TRG/SCI0_SCK/DISP_DATA15/SCIF3_SCK | — |

| 196 | IRQ3_A | 3.3V | P18_1/IRQ3/SCIF3_SCK/SCI0_TXD/DISP_DATA20/SCIF3_RXD | — |

| 198 | IRQ4_A | 3.3V | P18_2/IRQ4/RSPI0_CK/SCI0_SCK/SCIF3_RXD/SCI0_RXD/DISP_DATA21/SCIF3_TXD | — |

| 200 |