“MYZR-SAMA5-CB200 硬件介绍”的版本间的差异

(创建页面,内容为“= '''MY-SAMA5-CB200视图''' = ---- == '''正面视图''' == 文件:MY-SAMA5-CB200_1.1.0.1.png == '''背面视图''' == 文件:MY-SAMA5-CB200_1.2.0.1.png = '...”) |

|||

| (未显示同一用户的18个中间版本) | |||

| 第1行: | 第1行: | ||

| − | = ''' | + | <div> |

| + | |||

| + | = '''MYZR-SAMA5-CB200视图''' = | ||

---- | ---- | ||

| + | |||

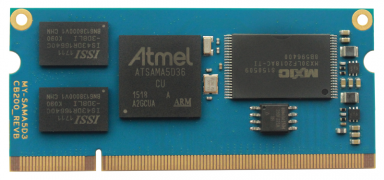

== '''正面视图''' == | == '''正面视图''' == | ||

| − | [[文件:MY-SAMA5-CB200_1.1.0.1.png]] | + | [[文件:MY-SAMA5-CB200_1.1.0.1.png|384px]] |

| + | |||

== '''背面视图''' == | == '''背面视图''' == | ||

| − | [[文件:MY-SAMA5-CB200_1.2.0.1.png]] | + | [[文件:MY-SAMA5-CB200_1.2.0.1.png|384px]] |

| + | |||

= '''SAMA5D3 MPU概览''' = | = '''SAMA5D3 MPU概览''' = | ||

---- | ---- | ||

== '''SAMA5D3简介''' == | == '''SAMA5D3简介''' == | ||

| − | + | Atmel | SMART SAMA5D3 MPU 能在低于 150mW 的功耗下提供高达 850DMIPS 的处理能力,是所有高性能、低功耗、成本敏感型工业应用的理想之选。其应用包括控制面板、智能电网设备和条形码扫描仪,即,需要高级别的连接性、增强的用户界面、稳定可靠的安全性或电池供电的任何设备。SAMA5D3 还是低功耗、小尺寸都至关重要的穿戴式计算应用和移动应用的理想之选。SAMA5D3 系列包括支持 -40/+105°C 温度范围以及 12x12mm BGA324 封装(间距为 0.5mm)的器件。<br> | |

| − | + | Atmel | SMART? SAMA5D3 系列以 536 Mhz 提供高达 850DMIPS 的处理能力,功耗水平市场领先(在工作模式下低于 150 mW;在低功耗模式下低于 0.5 mW)。通过支持高精度计算和快速数据处理的 FPU,以及 64 位内部总线架构和 32 位宽 DDR 控制器(能够以高达 166 MHz 的频率运行,提供高达 1328 MB/s 的带宽),实现了高性能。功能强大的外设包括多达三个的高速 USB 端口、千兆位和 10/100 以太网、双 CAN、TFT LCD 控制器、相机接口、三个 SDIO/SD/MMC、UART、SPI、TWI、软调制解调器、12 位 ADC、32 位定时器等。稳定可靠的安全性和防假冒由硬件加密引擎(如 AES/3DES、TRNG、SHA)和安全引导提供。这些器件随附免费 Atmel Linux? 分发包、Android 分发包、Qt SDK 以及一套完整的面向非操作系统用户的 C 示例。来自多个软件和硬件合作伙伴的 SOM(模块系统)、PMIC(电源管理IC)、内存和套件令本产品更加完整。<br> | |

== '''SAMA5D3优势''' == | == '''SAMA5D3优势''' == | ||

| − | * | + | *ARM Cortex-A5 内核以 536MHz (850DMIPS) 运行。<br> |

*用于高精度计算和快速数据处理的浮点运算单元 (FPU)。<br> | *用于高精度计算和快速数据处理的浮点运算单元 (FPU)。<br> | ||

*市场领先的低功耗优势<br> | *市场领先的低功耗优势<br> | ||

| 第24行: | 第29行: | ||

*AES/3DES 硬件加密引擎和安全引导。<br> | *AES/3DES 硬件加密引擎和安全引导。<br> | ||

*BGA324(15x15,间距为 0.8)封装,以及小封装选项 BGA(12x12mm,间距为 0.5)。<br> | *BGA324(15x15,间距为 0.8)封装,以及小封装选项 BGA(12x12mm,间距为 0.5)。<br> | ||

| − | * | + | *扩展的工业温度范围:-40°C 到 105°C。<br> |

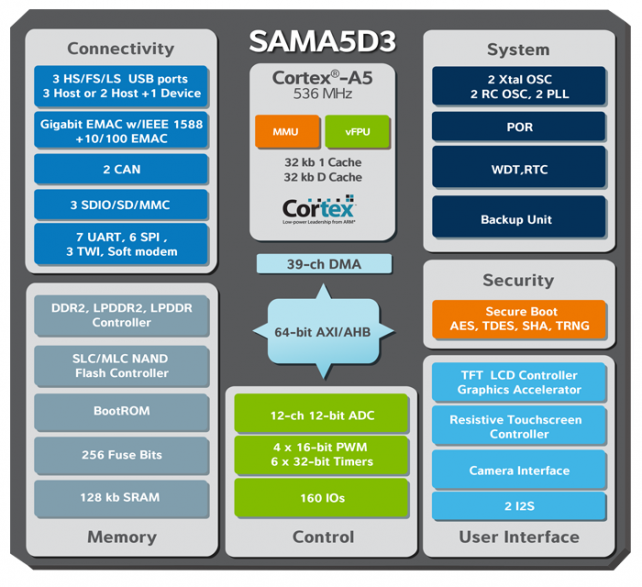

== '''SAMA5D3简图''' == | == '''SAMA5D3简图''' == | ||

| − | [[文件:MY-SAMA5-CB200_2.3.0.1.png]] | + | [[文件:MY-SAMA5-CB200_2.3.0.1.png|642px]] |

| + | |||

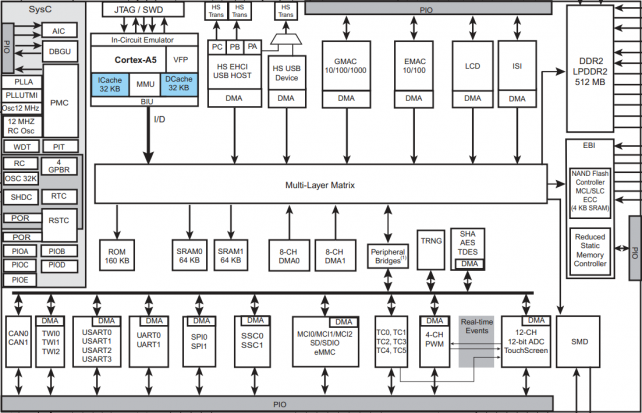

== '''SAMA5D3框图 ''' == | == '''SAMA5D3框图 ''' == | ||

| − | [[文件:MY-SAMA5-CB200_2.4.0.1.png]] | + | [[文件:MY-SAMA5-CB200_2.4.0.1.png|642px]] |

| + | |||

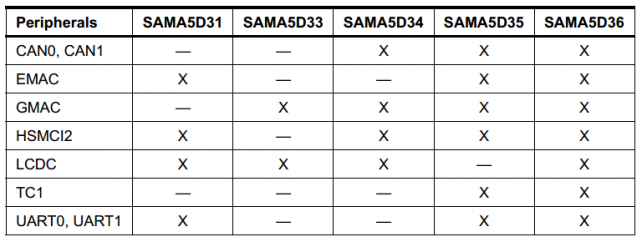

== '''SAMA5D3 MPU差异''' == | == '''SAMA5D3 MPU差异''' == | ||

| − | [[文件:MY-SAMA5-CB200_2.5.0.1.png]] | + | [[文件:MY-SAMA5-CB200_2.5.0.1.png|642px]] |

| + | |||

== '''SAMA5D36关键参数''' == | == '''SAMA5D36关键参数''' == | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | | | + | |Parameter |

|Value | |Value | ||

|- | |- | ||

| 第156行: | 第164行: | ||

|} | |} | ||

| − | = ''' | + | = '''SAMA5D3-CB200配置''' = |

== '''硬件配置''' == | == '''硬件配置''' == | ||

---- | ---- | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | | | + | |CPU |

|SAMA5D3x | |SAMA5D3x | ||

|工业级/扩展工业级 | |工业级/扩展工业级 | ||

|- | |- | ||

| − | |内存 | + | |内存 |

|256MB | |256MB | ||

|可扩展到512MB | |可扩展到512MB | ||

|- | |- | ||

| − | |存储 | + | |存储 |

|256MB | |256MB | ||

|最大可支持到2GB | |最大可支持到2GB | ||

| 第177行: | 第185行: | ||

|支持烧录 | |支持烧录 | ||

|- | |- | ||

| − | |启动模式 | + | |启动模式 |

| − | |SPI启动 | + | |SPI启动 |

|确保产品的稳定可靠 | |确保产品的稳定可靠 | ||

|} | |} | ||

| 第184行: | 第192行: | ||

== '''工作温度范围''' == | == '''工作温度范围''' == | ||

*工业级<br> | *工业级<br> | ||

| − | + | :::-40°C ~ 85°C<br> | |

| − | |||

| − | |||

== '''操作系统支持''' == | == '''操作系统支持''' == | ||

| − | * | + | *内核:Linux-3.18<br> |

| − | * | + | *界面:命令行,QT5<br> |

| + | |||

== '''型号命令''' == | == '''型号命令''' == | ||

=== 型号名称组成 === | === 型号名称组成 === | ||

| − | + | MYZR-SAMA5-CB200-MPU规格-内存容量-存储容量<br> | |

| − | === MPU规格 === | + | |

| + | === MPU规格=== | ||

D36ACN, D36ACNR: 工业扩展级<br> | D36ACN, D36ACNR: 工业扩展级<br> | ||

D36ACU, D36ACUR: 工业级<br> | D36ACU, D36ACUR: 工业级<br> | ||

| + | |||

=== 内存容量 === | === 内存容量 === | ||

256MB: 256兆内存<br> | 256MB: 256兆内存<br> | ||

| + | |||

=== 存储容量 === | === 存储容量 === | ||

256MB: 256兆存储<br> | 256MB: 256兆存储<br> | ||

| + | |||

=== 型号举例 === | === 型号举例 === | ||

| − | + | MYZR-SAMA5-CB200-D36ACN-256M-256M <br> | |

| − | = ''' | + | == '''硬件接口''' == |

| + | {| class="wikitable" | ||

| + | |- | ||

| + | |colspan=2|接口规格||最大可配置接口数||描述 | ||

| + | |- | ||

| + | |rowspan=7|通讯接口||Ethernet||2||1路10/100/1000Mbps以太网,1路10/100Mbps以太网 | ||

| + | |- | ||

| + | |USB2.0||3||3路HOST或2路HOST+1路DEVICE,速率高达480 Mbps | ||

| + | |- | ||

| + | |UART||7||6路应用串口,1路调试串口 | ||

| + | |- | ||

| + | |I2C||3||3路I2C,最高支持400 kbps | ||

| + | |- | ||

| + | |SPI||2||2路SPI | ||

| + | |- | ||

| + | |ADC||12||12通道12-bit分辨率 | ||

| + | |- | ||

| + | |PWM||4||4通道16bit计数器 | ||

| + | |- | ||

| + | |外部存储||SD/SDIO||2||4/8bit SD/SDIO V2.0 | ||

| + | |- | ||

| + | |rowspan=3|多媒体||RGB||1||最高支持24bit | ||

| + | |- | ||

| + | |SSC||2||2路 | ||

| + | |- | ||

| + | |ISI||1||12-bit Grayscale CMOS摄像头 | ||

| + | |} | ||

| + | |||

| + | = '''MYZR-SAMA5-CB200定义''' = | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | + | !序号 | |

| + | !引脚 | ||

| + | !默认信号 | ||

| + | !默认接口 | ||

| + | !可复用的信号 | ||

| + | ! | ||

| + | !可复用的信号 | ||

| + | !默认接口 | ||

| + | !默认信号 | ||

| + | !引脚 | ||

| + | !序号 | ||

|- | |- | ||

|1 ||GND_POWER || || || || || || || ||GND_POWER ||2 | |1 ||GND_POWER || || || || || || || ||GND_POWER ||2 | ||

| 第530行: | 第579行: | ||

|199 ||GND_POWER || || || || || || || ||VCC_3V3 ||200 | |199 ||GND_POWER || || || || || || || ||VCC_3V3 ||200 | ||

|- | |- | ||

| − | |colspan=11| | + | |colspan=11|说明1:“可复用的信号”栏中黄色背景表示在MYZR-SAMA5-EK200上实现的信号。<br> |

| + | |||

|- | |- | ||

| − | |colspan=11| | + | |colspan=11|说明2:MYZR-SAMA5-CB200-D36引出的管脚主要有PA0~PA31、PB0~PB31、PC0~PC31、PD0~PD12、PD14~PD31、PE0~PE20、PE23~PE31。<br> |

|} | |} | ||

| 第538行: | 第588行: | ||

---- | ---- | ||

== '''SAMA5关键亮点''' == | == '''SAMA5关键亮点''' == | ||

| − | === 高性能 === | + | === 高性能=== |

| − | + | SAMA5 系列是专为弥补 ARM Cortex-A5 内核在功率方面的不足而设计,包括的器件能以低至 150 mW 的功耗提供高达 945DMIPS 的处理能力。<br> | |

:*1.58 DMIPS/MHz ARM Cortex-A5 内核<br> | :*1.58 DMIPS/MHz ARM Cortex-A5 内核<br> | ||

:*高达 600 MHz 的最大工作频率 (945DMIPS)<br> | :*高达 600 MHz 的最大工作频率 (945DMIPS)<br> | ||

| 第548行: | 第598行: | ||

=== 低功耗 === | === 低功耗 === | ||

| − | + | SAMA5 器件采用创新技术以降低所有模式下的功耗,并且可实现:<br> | |

:*在激活所有外设的情况下,以低于 150mW 的功耗(在工作模式下)提供高达 536MHz 的工作频率<br> | :*在激活所有外设的情况下,以低于 150mW 的功耗(在工作模式下)提供高达 536MHz 的工作频率<br> | ||

| − | :*在运行 SRAM 和 寄存器保留的低功耗模式下,功耗低于 0.5mW 且唤醒时间短于 0. | + | :*在运行 SRAM 和 寄存器保留的低功耗模式下,功耗低于 0.5mW 且唤醒时间短于 0.5ms。在运行RTC(实时时钟)的备份模式下功耗约为 1.2μA<br> |

:*电池供电系统的理想之选<br> | :*电池供电系统的理想之选<br> | ||

=== 连接性 === | === 连接性 === | ||

| − | + | SAMA5 器件嵌入了各种高级通信外设,因此是网桥和网关的理想之选。<br> | |

:*支持 IEEE1588 的以太网 MAC 和千兆位以太网 MAC、双 CAN 端口<br> | :*支持 IEEE1588 的以太网 MAC 和千兆位以太网 MAC、双 CAN 端口<br> | ||

:*可配置为三个主机或两个主机及一个器件端口的三个高速 USB 端口<br> | :*可配置为三个主机或两个主机及一个器件端口的三个高速 USB 端口<br> | ||

| 第560行: | 第610行: | ||

=== 增强的用户界面 === | === 增强的用户界面 === | ||

| − | + | 使用 SAMA5 MPU,可以创建当今应用所需的时尚、平稳的用户界面。<br> | |

:*图形 LCD 控制器具有图像合成叠加和集成功能(如 α 混合、缩放、颜色转换和旋转)<br> | :*图形 LCD 控制器具有图像合成叠加和集成功能(如 α 混合、缩放、颜色转换和旋转)<br> | ||

:*720p 硬件视频解码器,用于加快支持当今主流视频标准的视频回放<br> | :*720p 硬件视频解码器,用于加快支持当今主流视频标准的视频回放<br> | ||

| 第567行: | 第617行: | ||

=== 安全 === | === 安全 === | ||

| − | + | SAMA5 系列包括防止克隆、确保真实性以及保护应用的通信和数据存储安全的功能。<br> | |

:*安全引导<br> | :*安全引导<br> | ||

:*硬件加密引擎,如高级加密标准 (AES)/三重数据加密标准 (DES)、RSA (Rivest-Shamir-Adleman) 和 ECC(椭圆曲线加密)以及安全哈希算法 (SHA) 和真正的随机号码生成器 (TRNG)<br> | :*硬件加密引擎,如高级加密标准 (AES)/三重数据加密标准 (DES)、RSA (Rivest-Shamir-Adleman) 和 ECC(椭圆曲线加密)以及安全哈希算法 (SHA) 和真正的随机号码生成器 (TRNG)<br> | ||

| 第576行: | 第626行: | ||

=== 安全性 === | === 安全性 === | ||

| − | + | SAMA5 系列具有的功能可轻松简便地实施如 IEC61508 等安全标准。<br> | |

:*主晶体振荡器时钟具有故障检测器<br> | :*主晶体振荡器时钟具有故障检测器<br> | ||

:*上电复位<br> | :*上电复位<br> | ||

| 第585行: | 第635行: | ||

:*Arm 信任区域<br> | :*Arm 信任区域<br> | ||

| − | === 低系统成本 === | + | === 低系统成本=== |

| − | + | SAMA5 凭借高度的系统集成,在实现最大灵活性的同时还减少了对其他昂贵组件的需求。<br> | |

:*0.8mm 球间距封装简化了 PCB 设计并降低了成本<br> | :*0.8mm 球间距封装简化了 PCB 设计并降低了成本<br> | ||

:*最低功耗方案,需要芯片离散的电源或低成本 PMIC<br> | :*最低功耗方案,需要芯片离散的电源或低成本 PMIC<br> | ||

| 第594行: | 第644行: | ||

:*集成的软调制解调器解决方案节省了外部调制解调器设备的成本<br> | :*集成的软调制解调器解决方案节省了外部调制解调器设备的成本<br> | ||

| − | == ''' | + | == '''SAMA5D3特性''' == |

| − | === | + | === 核心 === |

| − | :* | + | :*ARM Cortex-A5处理器与ARM v7-A Thumb2? 指令系统<br> |

| − | + | :**CPU频率最高可达536 MHz <br> | |

| − | + | :*32 KB数据高速缓存,32 KB指令高速缓存,虚拟内存系统架构(VMSA)<br> | |

| − | + | :*完全集成的MMU和浮点单元(VFPv4)<br> | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | :* | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | :* | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | :* | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | === | + | === 记忆 === |

| − | :* | + | :*一个160 KB的内部ROM单周期访问,系统速度,嵌入式启动加载器:8位启动。<br> |

| − | :* | + | :*NAND闪存、SDCard、eMMC、串行数据流?,选择 <br> |

| − | :* | + | :*一个128 KB的内部SRAM,系统速度下的单周期访问。<br> |

| − | :* | + | :*高带宽32位多端口动态RAM控制器支持512 Mbyte 8 bank DDR2 / LPDDR / LPDDR2与数据路径加扰。<br> |

| − | :* | + | :*独立静态存储器控制器,具有数据通路加扰和SLC / MLC NAND支持,最高可达24位纠错码(PMECC)。<br> |

| − | :* | + | === 系统运行频率高达166 MHz=== |

| − | === | + | :*复位控制器,关断控制器,周期性间隔定时器,看门狗定时器和实时时钟。<br> |

| − | :* | + | :*引导模式选择选项,重命名命令。<br> |

| − | :* | + | :*内部低功耗32 kHz RC振荡器和快速12 MHz RC振荡器。<br> |

| − | :** | + | :*可选32768 Hz低功耗振荡器和12 MHz振荡器。<br> |

| − | :** | + | :*一个用于系统的400至1000 MHz PLL和一个480 MHz的PLL优化d用于USB高速。<br> |

| − | :* | + | :*39个DMA通道,包括两个8通道64位的中央DMA控制器。br> |

| + | :*64位高级中断控制器。<br> | ||

| + | :*3个可编程的外部时钟信号。<br> | ||

| + | :*可编程保险丝盒,带256个熔丝位,其中192个可供客户使用。<br> | ||

| + | ===低功耗管理=== | ||

| + | :*关闭控制器<br> | ||

| + | :*电池备份寄存器 <br> | ||

| + | :*时钟脉冲发生器和电源管理控制器<br> | ||

| + | :*非常慢的时钟操作模式,软件可编程的功率优化能力<br> | ||

| + | ===外围设备 === | ||

| + | :*LCD TFT控制器具有叠加,Alpha混合,旋转,缩放和色彩空间转换<br> | ||

| + | :*ITU-R BT,601/656图像传感器接口<br> | ||

| + | :*3个HS/FS/LS USB端口和芯片上的收发器。<br> | ||

| + | :**一个设备控制器 <br> | ||

| + | :**一个带集成根集线器的主机控制器(3个下行端口)<br> | ||

| + | :*支持IEEE1588的一个10/100/1000 Mbps千兆以太网MAC控制器(GMAC)<br> | ||

| + | :*一个10/100 Mbps以太网MAC控制器(EMAC)<br> | ||

| + | :*两个CAN控制器,带有8个邮箱,完全符合CAN 2.0 A部分和2.0 B部分<br> | ||

| + | :*Softmodem接口<br> | ||

| + | :*三个高速存储卡主机(eMMC 4.3和SD 2.0)<br> | ||

| + | :*两个主/从串行外设接口<br> | ||

| + | :*两个同步串行控制器<br> | ||

| + | :*三个双线接口,最高400 Kbit / s,支持I2C协议和SMBUS<br> | ||

| + | :*四个USART,两个UART,一个DBGU <br> | ||

| + | :*两个三通道32位定时器/计数器<br> | ||

| + | :*一个4通道16位PWM控制器<br> | ||

| + | :*一个具有电阻式触摸屏功能的12通道12位模数转换器<br> | ||

| + | ===安全=== | ||

| + | :*上电复位单元<br> | ||

| + | :*独立看门狗<br> | ||

| + | :*主晶振时钟故障检测<br> | ||

| + | :*写保护寄存器<br> | ||

| + | :*SHA:支持安全散列算法(SHA1,SHA224,SHA 256,SHA384,SHA512)<br> | ||

| + | :*内存管理单元<br> | ||

| + | ===保密 === | ||

| + | :*TRNG:真正的随机数生成器<br> | ||

| + | :*加密引擎<br> | ||

| + | :**AES:256位,192位,128位密钥算法,符合FIPS PUB 197规范<br> | ||

| + | :**TDES:双键或三键算法,符合FIPS PUB 46-3规范<br> | ||

| + | :*Atmel? 安全启动解决方案<br> | ||

=== I/O === | === I/O === | ||

| − | :* | + | :*五个32位并行输入/输出控制器<br> |

| − | :*160 I/ | + | :* 160 I/O <br> |

| − | :* | + | :*输入改变每个I/O线上的中断能力,可选施密特触发器输入<br> |

| − | :* | + | :*可单独编程的开漏,上拉和下拉电阻,同步输出,滤波<br> |

| − | :* | + | :*高速I/O的转换速率控制<br> |

| − | :* | + | :* DDR I/O的阻抗控制<br> |

| − | === | + | === 程序包 === |

| − | :*324-ball LFBGA, 15 x 15 x 1.4 mm, | + | :*324-ball LFBGA, 15 x 15 x 1.4 mm, 间距 0.8 mm<br> |

| − | :*324-ball TFBGA, 12 x 12 x 1.2 mm, | + | :*324-ball TFBGA, 12 x 12 x 1.2 mm, 间距 0.5 mm<br> |

| − | == '''SAMA5D3 | + | == '''SAMA5D3 嵌入式特性''' == |

=== WDT === | === WDT === | ||

| − | : | + | :12位密钥保护可编程计数器<br> |

| − | :* | + | :*看门狗时钟独立于处理器时钟<br> |

| − | :* | + | :*为系统提供复位或中断信号<br> |

| − | :* | + | :*计数器可能在处理器处于调试状态或处于空闲模式时停止<br> |

=== RTC === | === RTC === | ||

| − | :* | + | :*超低功耗<br> |

| − | :* | + | :*完全异步设计<br> |

| − | :* | + | :*格里高利历直到2099年<br> |

| − | :* | + | :*可编程周期中断<br> |

| − | :* | + | :*安全/安全功能:<br> |

| − | :** | + | :**有效的时间和日期计划检查<br> |

| − | |||

=== PIO === | === PIO === | ||

| − | :* | + | :*最多32个可编程I/O线<br> |

| − | :* | + | :*可通过置位/清除寄存器完全编程<br> |

| − | :* | + | :*每个I/O线路复用四个外设功能<br> |

| − | :* | + | :*对于每个I/O线(是分配给外设还是用作通用I/O)<br> |

| − | :** | + | :**输入更改中断<br> |

| − | :** | + | :**可编程毛刺滤波器<br> |

| − | :** | + | :**可编程去噪滤波器<br> |

| − | :** | + | :**多驱动器选项可实现开漏式驱动<br> |

| − | :** | + | :**每个I/O线上的可编程上拉电阻<br> |

| − | :** | + | :**引脚数据状态寄存器,随时提供引脚电平的可见性<br> |

| − | :** | + | :**可编程事件的附加中断模式:上升沿,下降沿,低电平或高电平<br> |

| − | :** | + | :**通过连接的外围设备锁定配置<br> |

| − | :* | + | :*同步输出,在单次写入中提供几个I/O线的置位和清除 |

| − | :* | + | :*寄存器写保护<br> |

| − | :* | + | :*可编程施密特触发器输入<br> |

| − | :* | + | :*可编程I/O驱动器<br> |

=== LCDC === | === LCDC === | ||

| − | :* | + | :*双AHB主接口<br> |

| − | :* | + | :*支持单扫描有源TFT显示器<br> |

| − | :* | + | :*通过空间抖动单元支持12,16,18和24位输出模式<br> |

| − | :* | + | :*支持异步输出模式(在合成时)<br> |

| − | :* | + | :*每像素1,2,4,8位(托盘化)<br> |

| − | :*12, 16, 18, 19, 24, | + | :* 12,16,18,19,24,25和32位/像素(非托盘化)<br> |

| − | :* | + | :*支持一个基本层(背景)<br> |

| − | :* | + | :*支持两个叠加层Windows <br> |

| − | :* | + | :*支持一个高端覆盖(HEO)窗口<br> |

| − | :* | + | :*支持一个硬件光标,固定或自由尺寸<br> |

| − | :* | + | :*硬件光标固定大小在以下模式:32x32,64x64和128x128 <br> |

| − | :*Little Endian Memory Organization<br> | + | :* Little Endian Memory Organization <br> |

| − | :* | + | :*可编程定时引擎,带整数时钟分频器<br> |

| − | :* | + | :*数据的可编程极性,线同步和帧同步。<br> |

| − | :* | + | :*显示尺寸最大为2048x2048,或视频格式最高为720p <br> |

| − | :* | + | :*颜色查找表,最多256个条目和预定义的8位Alpha <br> |

| − | :* | + | :*可编程负和正行跨步所有图层<br> |

| − | :* | + | :*可编程负像素和正像素跨越所有Overlay1,Overlay2和HEO图层<br> |

| − | :* | + | :*高端覆盖支持4:2:0平面模式和半平面模式<br> |

| − | :* | + | :*高端覆盖支持4:2:2平面模式,半平面模式和Packed <br> |

| − | :* | + | :*高端覆盖包括色度上采样单元<br> |

| − | :* | + | :*具有边缘插值和独立非整数比的水平和垂直重定标单元<br> |

| − | :* | + | :*支持隐藏层删除。<br> |

| − | :* | + | :*集成完全可编程的色彩空间转换<br> |

| − | :* | + | :* Overlay1,Overlay2和High End Overlay集成旋转引擎:90,180,270 <br> |

| − | :* | + | :* Blender功能支持任意8位Alpha值和色度键控<br> |

| − | :* | + | :* DMA用户界面使用链接列表结构和添加到队列结构<br> |

=== ISI === | === ISI === | ||

| − | :*ITU-R | + | :* ITU-R BT,601/656 8位模式外部接口支持<br> |

| − | :* | + | :*支持最高12位灰度CMOS传感器<br> |

| − | :* | + | :*支持ITU-R BT.656-4 SAV和EAV同步<br> |

| − | :* | + | :*垂直和水平分辨率高达2048 * 2048 <br> |

| − | :* | + | :*预览路径<br> |

| − | :** | + | :**灰度模式下最高可达2048 * 2048 <br> |

| − | :** | + | :** RGB模式下最高640 * 480 |

| − | :* | + | :* Codec Path上的32字节FIFO <br> |

| − | :* | + | :*预览路径上的32字节FIFO <br> |

| − | :* | + | :*支持YCbCr 4:2:2 Formats <br>的打包数据格式 |

| − | :* | + | :*预览缩放器以生成更小的图像<br> |

| − | :* | + | :*可编程帧捕获率<br> |

| − | :* | + | :*支持LCD预览的VGA,QVGA,CIF,QCIF格式<br> |

| − | :* | + | :*自定义格式,水平和垂直预览大小为16的倍数也支持LCD预览< |

=== UDPHS === | === UDPHS === | ||

| − | :* | + | :* 1设备高速<br> |

| − | :* | + | :* 1主机和设备之间共享的UTMI收发器 |

| − | :*USB v2. | + | :* USB v2.0高速兼容,480Mbit/s <br> |

| − | :* | + | :* 16个端点,最多1024个字节<br> |

| − | :* | + | :*用于端点的嵌入式双端口RAM <br> |

| − | :* | + | :*暂停/恢复逻辑(UTMI的命令)<br> |

| − | :* | + | :*最多三个内存组用于端点(不适用于控制端点)<br> |

| − | :*8 | + | :* 8 KB的DPRAM <br> |

=== UHPHS === | === UHPHS === | ||

| − | :* | + | :*符合增强型HCI Rev 1.0规范<br> |

| − | :** | + | :**符合USB V2.0高速<br> |

| − | :** | + | :**支持高速480 Mbps <br> |

| − | :* | + | :*符合OpenHCI Rev 1.0规范<br> |

| − | :** | + | :**符合USB V2.0全速和低速规格<br> |

| − | :** | + | :**支持低速1.5 Mbps和全速12 Mbps USB设备<br> |

| − | :*Root | + | :* Root Hub集成了3个下行USB HS端口<br> |

| − | :* | + | :*嵌入式USB收发器<br> |

| − | :* | + | :*支持电源管理<br> |

| − | :* | + | :*主机(A和B)高速(EHCI),端口A与UDPHS共享 |

=== GMAC === | === GMAC === | ||

| − | :* | + | :*与IEEE标准802.3兼容 |

| − | :*10, | + | :* 10,100和1000 Mbps操作<br> |

| − | :* | + | :*在所有支持的操作速度下完全和半双工操作<br> |

| − | :* | + | :* RMON / MIB的统计计数器寄存器<br> |

| − | :* | + | :*物理层的MII / GMII / RGMII接口<br> |

| − | :* | + | :*集成物理编码<br> |

| − | :* | + | :*直接内存访问(DMA)接口到外部存储器<br> |

| − | :* | + | :* DMA的可编程突发长度和字节序 |

| − | :* | + | :*中断生成以指示接收和发送完成,或错误<br> |

| − | :* | + | :*在传输帧上自动填充和循环冗余校验(CRC)生成<br> |

| − | :* | + | :*半双工模式下帧扩展和帧突发1000 Mbps <br> |

| − | :* | + | :*自动丢弃收到错误的帧<br> |

| − | :* | + | :*接收和传输IP,TCP和UDP校验和卸载。支持IPv4和IPv6数据包类型 |

| − | :* | + | :*地址检查逻辑,用于四个特定的48位地址,四种类型ID,混杂模式,<br>的哈希匹配 |

| − | :* | + | :*单播和多播目标地址和局域网唤醒<br> |

| − | :* | + | :*物理层管理的管理数据输入/输出(MDIO)接口<br> |

| − | :* | + | :*支持最大10240字节的巨型帧 |

| − | :* | + | :*全双工流量控制,识别传入暂停帧和硬件生成传输暂停<br> |

| − | :* | + | :*帧点击 |

| − | :* | + | :*通过强制传入帧上的冲突来实现半双工流量控制 |

| − | :* | + | :*支持802.1Q VLAN标记,识别传入VLAN和优先级标记帧<br> |

| − | :* | + | :*支持基于802.1Qbb优先级的流量控制<br> |

| − | :* | + | :*可编程数据包间隙(IPG)拉伸<br> |

| − | :* | + | :* IEEE 1588 PTP帧的识别<br> |

| − | :*IEEE | + | :* IEEE 1588时间戳单元(TSU)<br> |

| − | :* | + | :*支持802.1AS定时和同步<br> |

=== EMAC === | === EMAC === | ||

| − | :* | + | :*支持物理层的RMII接口<br> |

| − | :* | + | :*与IEEE标准802.3兼容 |

| − | :* | + | :* 10和100 Mbit / s操作<br> |

| − | :* | + | :*全双工和半双工操作<br> |

| − | :* | + | :*统计计数器寄存器<br> |

| − | :* | + | :*中断生成到信号接收和发送完成<br> |

| − | :* | + | :* DMA主接收和发送通道<br> |

| − | :* | + | :*发送和接收FIFO <br> |

| − | :* | + | :*传输帧上的自动填充和CRC生成<br> |

| − | :* | + | :*自动丢弃因错??误而收到的帧<br> |

| − | :* | + | :*地址检查逻辑支持最多四个特定的48位地址<br> |

| − | :* | + | :*支持混杂模式,其中所有有效接收帧都复制到内存<br> |

| − | :* | + | :*单播和多播目标地址的哈希匹配<br> |

| − | :* | + | :*通过MDIO接口进行物理层管理<br> |

| − | :* | + | :*通过强制进入帧的冲突实现半双工流控制<br> |

| − | :* | + | :*具有识别输入暂停帧的全双工流量控制<br> |

| − | :* | + | :*支持802.1Q VLAN标记,识别入局VLAN和优先级标记帧<br> |

| − | :* | + | :*每个接收和发送帧多个缓冲区<br> |

| − | :* | + | :*局域网唤醒支持<br> |

| − | :* | + | :* Jumbo帧最多支持10240字节<br> |

| − | === HSMCI === | + | === HSMCI === |

| − | :* | + | :*兼容多媒体卡规范版本4.3 <br> |

| − | :* | + | :*兼容SD存储卡规范版本2.0 <br> |

| − | :* | + | :*兼容SDIO规范版本2.0 <br> |

| − | :* | + | :*与CE-ATA规范1.1兼容 |

| − | :* | + | :*卡时钟速率高达主时钟除以2 <br> |

| − | :* | + | :*引导操作模式支持<br> |

| − | :* | + | :*高速模式支持<br> |

| − | :* | + | :*嵌入式电源管理,在不使用时降低时钟速率<br> |

| − | :* | + | :*支持1个多路复用插槽<br> |

| − | :** | + | :**每个插槽用于高速多媒体卡总线(最多30个卡)或SD存储卡<br> |

| − | :* | + | :*支持流,块和多块数据读写 |

| − | :* | + | :*支持连接到DMA控制器(DMAC)<br> |

| − | :** | + | :**最大限度地减少大型缓冲区传输的处理器干预<br> |

| − | :* | + | :*内置FIFO(16至256字节),大内存孔径支持增量访问<br> |

| − | :* | + | :*支持CE-ATA完成信号禁用命令<br> |

| − | :* | + | :*防止配置寄存器的即时修改意外<br> |

| − | === SPI === | + | === SPI === |

| − | :* | + | :*支持与串行外部设备通信<br> |

| − | :** | + | :**主模式可以将SPCK驱动到外设时钟(以最大总线时钟除以2为限) |

| − | :** | + | :**从模式在SPCK上运行,与核心和总线时钟异步 |

| − | :** | + | :**具有外部解码器支持的四个芯片选择允许与多达15个外设进行通信<br> |

| − | :** | + | :**串行存储器,如DataFlash和3线EEPROM <br> |

| − | :** | + | :**串行外设,如ADC,DAC,LCD控制器,CAN控制器和传感器<br> |

| − | :** | + | :**外部协处理器<br> |

| − | :* | + | :*主或从串行外设总线接口<br> |

| − | :** | + | :**每片8位至16位可编程数据长度选择<br> |

| − | :** | + | :**每个芯片的可编程相位和极性选择<br> |

| − | :** | + | :**每个芯片SPI时钟选择之前的可连续传输和延迟之间的可编程传输延迟 |

| − | :** | + | :**芯片选择之间的可编程延迟<br> |

| − | :** | + | :**可选模式故障检测<br> |

| − | :* | + | :*与DMA通道功能的连接优化数据传输<br> |

| − | :** | + | :**接收器的一个通道,发送器的一个通道<br> |

| − | === TWI === | + | === TWI === |

| − | :*3 TWIs <br> | + | :* 3 TWIs <br> |

| − | :* | + | :*兼容Atmel双线接口串行存储器和I2C兼容设备<br> |

| − | :* | + | :*从属地址的一个,两个或三个字节<br> |

| − | :* | + | :*顺序读写操作<br> |

| − | :* | + | :* Master,Multi-master和Slave Mode Operation <br> |

| − | :* | + | :*比特率:高达400 Kbit / s <br> |

| − | :* | + | :*从属模式支持的一般呼叫<br> |

| − | :* | + | :*主模式支持的SMBUS快速命令<br> |

| − | :* | + | :*与DMA控制器(DMA)通道功能的连接优化数据传输<br> |

| − | === SSC === | + | |

| − | :* | + | === SSC === |

| − | :* | + | :*提供用于音频和电信应用的串行同步通信链路<br> |

| − | :* | + | :*包含独立接收器和发送器以及公共时钟分频器<br> |

| − | :* | + | :*与DMA控制器(DMAC)接口以减少处理器开销<br> |

| − | :* | + | :*提供可配置的帧同步和数据长度<br> |

| − | :* | + | :*接收器和发射器可以编程为自动启动或检测到不同事件<br> |

| − | :* | + | :*帧同步信号<br> |

| − | === DBGU === | + | :*接收器和发送器包括数据信号,时钟信号和帧同步信号<br> |

| − | :* | + | === DBGU === |

| − | :* | + | :*系统外设,以促进Atmel的调试?基于ARM?的系统<br> |

| − | :** | + | :*由四个函数组成<br> |

| − | :** | + | :**双引脚UART <br> |

| − | :** | + | :**调试通信通道(DCC)支持<br> |

| − | :** | + | :**芯片ID寄存器<br> |

| − | :* | + | :** ICE访问预防<br> |

| − | :** | + | :*双引脚UART <br> |

| − | :** | + | :**已实现的功能是USART兼容的<br> |

| − | :** | + | :**具有通用可编程波特率发生器的独立接收器和发送器<br> |

| − | :** | + | :**偶数,奇数,标记或空间奇偶生成<br> |

| − | :** | + | :**奇偶校验,成帧和溢出错误检测<br> |

| − | :** | + | :**自动回声,本地环回和远程环回信道模式<br> |

| − | :** | + | :**中断生成<br> |

| − | :* | + | :**支持连接到接收器和发送器的两个DMA通道<br> |

| − | :** | + | :*调试通信渠道支持<br> |

| − | :** | + | :**提供来自ARM处理器的COMMRX和COMM TX信号的可见性 |

| − | :* | + | :**中断生成<br> |

| − | :** | + | :*芯片ID注册<br> |

| − | :* | + | :**设备版本的识别,嵌入式存储器的大小,外围设备集<br> |

| − | :** | + | :* ICE访问预防<br> |

| − | :** | + | :**使软件能够通过ARM处理器的ICE防止系统访问 |

| − | === UART === | + | :**通过断言ARM处理器的ICE的NTRST线进行预防 |

| − | :* | + | === UART === |

| − | :** | + | :*双引脚UART <br> |

| − | :** | + | :**具有通用可编程波特率发生器的独立接收器和发送器<br> |

| − | :** | + | :**偶数,奇数,标记或空间奇偶生成<br> |

| − | :** | + | :**奇偶校验,成帧和溢出错误检测<br> |

| − | :** | + | :**自动回声,本地环回和远程环回信道模式<br> |

| − | :** | + | :**中断生成<br> |

| − | === USART === | + | :**支持连接到接收器和发送器的两个DMA通道<br> |

| − | :* | + | === USART === |

| − | :* | + | :*可编程波特率发生器<br> |

| − | :** | + | :* 5至9位全双工同步或异步串行通信<br> |

| − | :** | + | :**异步模式下的1个,1.5个或2个停止位或同步模式下的1个或2个停止位 |

| − | :** | + | :**奇偶校验生成和错误检测<br> |

| − | :**MSB- | + | :**帧错误检测,溢出错误检测<br> |

| − | :** | + | :** MSB-或LSB-first <br> |

| − | :** | + | :**可选的中断生成和检测<br> |

| − | :** | + | :** 8或16过采样接收器频率<br> |

| − | :** | + | :**可选硬件握手RTS-CTS <br> |

| − | :** | + | :**接收器超时和发射器Timeguard <br> |

| − | :* | + | :**带地址生成和检测的可选多点模式<br> |

| − | :* | + | :*带驱动器控制信号的RS485 <br> |

| − | :** | + | :* ISO7816,T = 0或T = 1与智能卡接口的协议<br> |

| − | :** | + | :** NACK处理,具有重复和迭代限制的错误计数器<br> |

| − | :** | + | :** IrDA调制和解调<br> |

| − | :* | + | :**通信速率高达115.2 Kbps <br> |

| − | :** | + | :* SPI模式<br> |

| − | :** | + | :**主人或奴隶<br> |

| − | :** | + | :**串行时钟可编程相位和极性<br> |

| − | :* | + | :** SPI串行时钟(SCK)频率高达内部时钟频率MCK / 6 <br> |

| − | :** | + | :*测试模式<br> |

| − | :* | + | :**远程环回,本地环回,自动回声<br> |

| − | :** | + | :*支持连接:<br> |

| − | :* | + | :**两个DMA控制器通道(DMAC)<br> |

| − | === CAN === | + | :*提供无处理器干预的缓冲区传输<br> |

| − | :* | + | === CAN === |

| − | :* | + | :*完全符合CAN 2.0 A部分和2.0 B部分<br> |

| − | :* | + | :*比特率高达1 Mbit / s <br> |

| − | :** | + | :* 8个具有以下属性的面向对象的邮箱:<br> |

| − | :** | + | :** CAN规范2.0 A部分或2.0 B部分可编程为每个消息<br> |

| − | :** | + | :**对象可在接收(具有覆盖或不覆盖)或发送模式中配置<br> |

| − | :** | + | :**为每个邮箱定义独立的29位标识符和掩码<br> |

| − | :** | + | :**每个邮箱数据对象的32位数据寄存器访问<br> |

| − | :** | + | :**在接收和发送消息时使用16位时间戳<br> |

| − | :* | + | :** ID屏蔽位域的硬件级联,以加快系列ID处理<br> |

| − | :* | + | :*用于时间戳和网络同步的16位内部定时器<br> |

| − | :* | + | :*可编程接收缓冲区长度最多8个邮箱对象<br> |

| − | :* | + | :*传输邮箱之间的优先级管理<br> |

| − | :* | + | :* Autobaud和Listening Mode <br> |

| − | :* | + | :*低功耗模式和可编程唤醒总线活动或应用程序<br> |

| − | :* | + | :*数据,远程,错误和过载帧处理<br> |

| − | === PWM === | + | :*写保护寄存器<br> |

| − | :* | + | === PWM === |

| − | :* | + | :*频道点击 |

| − | :** | + | :*通用时钟发生器提供十三种不同的时钟<br> |

| − | :** | + | :**提供十一个时钟的模数计数器<br> |

| − | :* | + | :**两个独立的线性分频器工作模数n计数器输出<br> |

| − | :** | + | :*独立频道<br> |

| − | :** | + | :**每个通道独立的16位计数器<br> |

| − | :** | + | :**每个通道的12位死区发生器(也称为死区或非重叠时间)的独立互补输出<br> |

| − | :** | + | :**每个通道的独立启用禁用命令<br> |

| − | :** | + | :**每个通道的独立时钟选择<br> |

| − | :** | + | :**每个频道的独立时段,占空比和死区时间<br> |

| − | :** | + | :**每个通道的周期,占空比和死区的独立双缓冲<br> |

| − | :** | + | :**独立可编程选择每个通道的输出波形极性<br> |

| − | :** | + | :**每个通道的独立可编程中心或左对齐输出波形<br> |

| − | :** | + | :**每个通道的独立输出覆盖<br> |

| − | :* | + | :**每个通道的独立中断,在每个周期进行左对齐或中心对齐配置<br> |

| − | :* | + | :* 2步进电机控制的2位灰色上/下通道<br> |

| − | :** | + | :*同步信道模式<br> |

| − | :** | + | :**同步通道共享同一个计数器<br> |

| − | :* | + | :**在可编程周期数后更新同步通道寄存器的模式<br> |

| − | :** | + | :* 2个用于同步ADC转换的独立事件行<br> |

| − | :* | + | :**事件线的可编程延迟,以延迟ADC测量<br> |

| − | :* | + | :* 8个用于在事件线上产生中断,脉冲的比较单元<br> |

| − | :** | + | :* 1可编程故障/中断输入提供PWM输出的异步保护<br> |

| − | :** | + | :** 4用户通过PIO输入驱动<br> |

| − | :** | + | :**当晶体振荡器时钟失效时PMC驱动<br> |

| − | :* | + | :** ADC控制器通过可配置比较功能驱动<br> |

| − | === ADC === | + | :*写保护寄存器<br> |

| − | :* | + | === ADC === |

| − | :*1 | + | :* 12位分辨率<br> |

| − | :* | + | :* 1 MHz转换率<br> |

| − | :* | + | :*宽范围电源操作<br> |

| − | :* | + | :*可选择单端或差分输入电压<br> |

| − | :* | + | :*可编程增益,用于最大满量程输入范围0 - VDD <br> |

| − | :** | + | :*电阻式4线和5线触摸屏控制器<br> |

| − | :** | + | :** 4线屏幕的位置和压力??测量<br> |

| − | :** | + | :** 5线屏幕的位置测量<br> |

| − | :* | + | :**噪声滤波最多8个平均值的平均值 |

| − | :* | + | :*可编程笔检测灵敏度<br> |

| − | :* | + | :*集成多路复用器,提供多达12个独立模拟输入<br> |

| − | :* | + | :*单个启用和禁用每个通道<br> |

| − | :** | + | :*硬件或软件触发器<br> |

| − | :** | + | :**外部触发引脚<br> |

| − | :** | + | :**定时器计数器输出(对应的TIOA触发器)<br> |

| − | :** | + | :**内部触发计数器<br> |

| − | :** | + | :**笔触点检测触发<br> |

| − | :* | + | :** PWM事件线<br> |

| − | :* | + | :* PWM故障输入驱动<br> |

| − | :* | + | :* DMA支持<br> |

| − | :* | + | :* ADC时序配置的可能性<br> |

| − | :** | + | :*两种睡眠模式和转换序列器<br> |

| − | :** | + | :**在所有启用的通道转换后,触发和返回睡眠模式下的自动唤醒<br> |

| − | :* | + | :**自定义频道序列的可能性<br> |

| − | :** | + | :*快速唤醒时间响应的待机模式<br> |

| − | :* | + | :**断电能力<br> |

| − | :** | + | :*转换值的自动窗口比较<br> |

| + | :**写保护寄存器<br> | ||

| + | |||

| + | </div> | ||

2022年4月21日 (四) 11:32的最新版本

目录

MYZR-SAMA5-CB200视图

正面视图

背面视图

SAMA5D3 MPU概览

SAMA5D3简介

Atmel | SMART SAMA5D3 MPU 能在低于 150mW 的功耗下提供高达 850DMIPS 的处理能力,是所有高性能、低功耗、成本敏感型工业应用的理想之选。其应用包括控制面板、智能电网设备和条形码扫描仪,即,需要高级别的连接性、增强的用户界面、稳定可靠的安全性或电池供电的任何设备。SAMA5D3 还是低功耗、小尺寸都至关重要的穿戴式计算应用和移动应用的理想之选。SAMA5D3 系列包括支持 -40/+105°C 温度范围以及 12x12mm BGA324 封装(间距为 0.5mm)的器件。

Atmel | SMART? SAMA5D3 系列以 536 Mhz 提供高达 850DMIPS 的处理能力,功耗水平市场领先(在工作模式下低于 150 mW;在低功耗模式下低于 0.5 mW)。通过支持高精度计算和快速数据处理的 FPU,以及 64 位内部总线架构和 32 位宽 DDR 控制器(能够以高达 166 MHz 的频率运行,提供高达 1328 MB/s 的带宽),实现了高性能。功能强大的外设包括多达三个的高速 USB 端口、千兆位和 10/100 以太网、双 CAN、TFT LCD 控制器、相机接口、三个 SDIO/SD/MMC、UART、SPI、TWI、软调制解调器、12 位 ADC、32 位定时器等。稳定可靠的安全性和防假冒由硬件加密引擎(如 AES/3DES、TRNG、SHA)和安全引导提供。这些器件随附免费 Atmel Linux? 分发包、Android 分发包、Qt SDK 以及一套完整的面向非操作系统用户的 C 示例。来自多个软件和硬件合作伙伴的 SOM(模块系统)、PMIC(电源管理IC)、内存和套件令本产品更加完整。

SAMA5D3优势

- ARM Cortex-A5 内核以 536MHz (850DMIPS) 运行。

- 用于高精度计算和快速数据处理的浮点运算单元 (FPU)。

- 市场领先的低功耗优势

- 在激活所有外设的情况下,以低于 150mW 的功耗(在工作模式下)提供高达 536MHz 的工作频率。

- 在具有 SRAM 和寄存器保留的情况下,低功耗模式下的功耗低于 0.5mW。

- 双 CAN 控制器。

- 在激活所有外设的情况下,以低于 150mW 的功耗(在工作模式下)提供高达 536MHz 的工作频率。

- 支持 IEEE1588 的千兆位以太网 MAC 和 10/100 MAC。

- 三个 HS 高速 USB 端口(可配置为三个主机或两个主机和一个器件端口)。

- CMOS 图像传感器接口。

- 图形 LCD 控制器,具有图像合成叠加

- AES/3DES 硬件加密引擎和安全引导。

- BGA324(15x15,间距为 0.8)封装,以及小封装选项 BGA(12x12mm,间距为 0.5)。

- 扩展的工业温度范围:-40°C 到 105°C。

SAMA5D3简图

SAMA5D3框图

SAMA5D3 MPU差异

SAMA5D36关键参数

| Parameter | Value |

| Pin Count: | 324 |

| Max. Operating Freq. (MHz): | 536 MHz |

| CPU: | Cortex-A5 |

| Max I/O Pins: | 160 |

| Ext Interrupts: | 160 |

| USB Transceiver: | 3 |

| USB Speed: | Hi-Speed |

| USB Interface: | Host, Device |

| SPI: | 6 |

| TWI (I2C): | 3 |

| UART: | 7 |

| CAN: | 2 |

| LIN: | 4 |

| SSC: | 2 |

| Ethernet: | 2 |

| SD / eMMC: | 3 |

| Graphic LCD: | Yes |

| Camera Interface: | Yes |

| ADC Channels: | 12 |

| ADC Resolution (bits): | 12 |

| ADC Speed (ksps): | 1000 |

| Resistive Touch Screen: | Yes |

| Crypto Engine: | AES/DES/SHA/TRNG |

| SRAM (Kbytes): | 128 |

| External Bus Interface: | 1 |

| DRAM Memory: | DDR2/LPDDR/LPDDR2 |

| NAND Interface: | Yes |

| Temp. Range (deg C): | -40 to 105 |

| I/O Supply Class: | 1.8/3.3 |

| Operating Voltage (Vcc): | 1.08 to 1.32 |

| FPU: | Yes |

| Timers: | 6 |

| Output Compare Channels: | 6 |

| Input Capture Channels: | 6 |

| PWM Channels: | 4 |

| 32kHz RTC: | Yes |

| MPU / MMU: | No / Yes |

| Quadrature Decoder Channels: | 0 |

| Video Decoder: | No |

SAMA5D3-CB200配置

硬件配置

| CPU | SAMA5D3x | 工业级/扩展工业级 |

| 内存 | 256MB | 可扩展到512MB |

| 存储 | 256MB | 最大可支持到2GB |

| SPI Flash | 2M | 支持烧录 |

| 启动模式 | SPI启动 | 确保产品的稳定可靠 |

工作温度范围

- 工业级

- -40°C ~ 85°C

- -40°C ~ 85°C

操作系统支持

- 内核:Linux-3.18

- 界面:命令行,QT5

型号命令

型号名称组成

MYZR-SAMA5-CB200-MPU规格-内存容量-存储容量

MPU规格

D36ACN, D36ACNR: 工业扩展级

D36ACU, D36ACUR: 工业级

内存容量

256MB: 256兆内存

存储容量

256MB: 256兆存储

型号举例

MYZR-SAMA5-CB200-D36ACN-256M-256M

硬件接口

| 接口规格 | 最大可配置接口数 | 描述 | |

| 通讯接口 | Ethernet | 2 | 1路10/100/1000Mbps以太网,1路10/100Mbps以太网 |

| USB2.0 | 3 | 3路HOST或2路HOST+1路DEVICE,速率高达480 Mbps | |

| UART | 7 | 6路应用串口,1路调试串口 | |

| I2C | 3 | 3路I2C,最高支持400 kbps | |

| SPI | 2 | 2路SPI | |

| ADC | 12 | 12通道12-bit分辨率 | |

| PWM | 4 | 4通道16bit计数器 | |

| 外部存储 | SD/SDIO | 2 | 4/8bit SD/SDIO V2.0 |

| 多媒体 | RGB | 1 | 最高支持24bit |

| SSC | 2 | 2路 | |

| ISI | 1 | 12-bit Grayscale CMOS摄像头 | |

MYZR-SAMA5-CB200定义

| 序号 | 引脚 | 默认信号 | 默认接口 | 可复用的信号 | 可复用的信号 | 默认接口 | 默认信号 | 引脚 | 序号 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | GND_POWER | GND_POWER | 2 | |||||||

| 3 | PC1 | ETX1 | EMAC | TIOB3 | LCDDAT19 | MCI2 | MCI2_DA0 | PC11 | 4 | |

| 5 | PC8 | EMDC | TCLK5 | LCDDAT18|TIOA1 | MCI2_DA1 | PC12 | 6 | |||

| 7 | PC3 | ERX1 | TIOA4 | LCDDAT21|PCK2 | MCI2_CK | PC15 | 8 | |||

| 9 | PC6 | ERXER | TIOA5 | LCDDAT17|TIOB1 | MCI2_DA2 | PC13 | 10 | |||

| 11 | PC4 | ETXEN | TIOB4 | LCDDAT20 | MCI2_CDA | PC10 | 12 | |||

| 13 | PC7 | EREFCK | TIOB5 | LCDDAT16|TCLK1 | MCI2_DA3 | PC14 | 14 | |||

| 15 | PC0 | ETX0 | TIOA3 | SSC0 | RK0 | PC19 | 16 | |||

| 17 | PC2 | ERX0 | TCLK3 | TF0 | PC17 | 18 | ||||

| 19 | PC5 | ECRSDV | TCLK4 | RF0 | PC20 | 20 | ||||

| 21 | PC9 | EMDIO | RD0 | PC21 | 22 | |||||

| 23 | PC30 | UTXD0 | UART0 | ISI_PCK | TK0 | PC16 | 24 | |||

| 25 | PC29 | URXD0 | ISI_D8|PWMFI2 | TD0 | PC18 | 26 | ||||

| 27 | GND_POWER | GND_POWER | 28 | |||||||

| 29 | PC31 | PWMFI1|FIQ | LCDC | LCDVSYNC | PA26 | 30 | ||||

| 31 | PC23 | SPI1_MOSI | SPI1 | LCDDISP | PA25 | 32 | ||||

| 33 | PC25 | SPI1_NPCS0 | GND_POWER | 34 | ||||||

| 35 | PC22 | SPI1_MISO | LCDC | LCDHSYNC | PA27 | 36 | ||||

| 37 | PC24 | SPI1_SPCK | GND_POWER | 38 | ||||||

| 39 | PC28 | SPI1_NPCS3 | ISI_D9|PWMFI0 | LCDC | LCDDEN | PA29 | 40 | |||

| 41 | PA4 | LCDDAT4 | LCDC | LCDDAT2 | PA2 | 42 | ||||

| 43 | PA10 | LCDDAT10 | LCDDAT15 | PA15 | 44 | |||||

| 45 | PA14 | LCDDAT14 | ISI_D1 | LCDDAT17 | PA17 | 46 | ||||

| 47 | PA12 | LCDDAT12 | LCDDAT1 | PA1 | 48 | |||||

| 49 | PA24 | LCDPWM | LCDDAT0 | PA0 | 50 | |||||

| 51 | PA22 | LCDDAT22 | ISI_D6|PWMH1 | LCDDAT3 | PA3 | 52 | ||||

| 53 | PA28 | LCDPCK | LCDDAT8 | PA8 | 54 | |||||

| 55 | PA20 | LCDDAT20 | ISI_D4|PWMH0 | LCDDAT6 | PA6 | 56 | ||||

| 57 | PA21 | LCDDAT21 | ISI_D5|PWML0 | ISI_D2|TWD2 | LCDDAT18 | PA18 | 58 | |||

| 59 | PA23 | LCDDAT23 | ISI_D7|PWML1 | ISI_D0 | LCDDAT16 | PA16 | 60 | |||

| 61 | PA5 | LCDDAT5 | ISI_D3|TWCK2 | LCDDAT19 | PA19 | 62 | ||||

| 63 | PA7 | LCDDAT7 | LCDDAT11 | PA11 | 64 | |||||

| 65 | PA30 | TWD0 | TWI0 | URXD1|ISI_VSYNC | LCDDAT9 | PA9 | 66 | |||

| 67 | PA31 | TWCK0 | UTXD1|ISI_HSYNC | LCDDAT13 | PA13 | 68 | ||||

| 69 | PD31 | PCK1|AD11 | ISI_D10|SPI1_NPCS2 | TWI1 | TWCK1 | PC27 | 70 | |||

| 71 | PD30 | PCK0 | SSC0:CLK | AD10 | ISI_D11|SPI1_NPCS1 | TWD1 | PC26 | 72 | ||

| 73 | PD29 | AD9 | AD | MCI0 | MCI0_DA3 | PD4 | 74 | |||

| 75 | PD28 | AD8 | MCI0_DA1 | PD2 | 76 | |||||

| 77 | PD27 | AD7 | MCI0_CDA | PD0 | 78 | |||||

| 79 | PD26 | AD6 | MCI0_CK | PD9 | 80 | |||||

| 81 | PD23 | AD3 | MCI0_DA2 | PD3 | 82 | |||||

| 83 | PD22 | AD2 | MCI0_DA0 | PD1 | 84 | |||||

| 85 | PD24 | AD4 | PWML2|TIOB0 | MCI0_DA5 | PD6 | 86 | ||||

| 87 | PD21 | AD1 | PWML3 | MCI0_DA7 | PD8 | 88 | ||||

| 89 | PD25 | AD5 | SPI0_NPCS2|CTS0 | CAN0 | CANTX0 | PD15 | 90 | |||

| 91 | PD20 | AD0 | SPI0_NPCS1|SCK0 | CANRX0 | PD14 | 92 | ||||

| 93 | PD5 | PWMH2 | PWM | MCI0_DA4|TIOA0 | UART0 | TXD0 | PD18 | 94 | ||

| 95 | PD7 | PWMH3 | MCI0_DA6|TCLK0 | RXD0 | PD17 | 96 | ||||

| 97 | PD19 | GPIO | ADTRG | SPI0 | SPI0_MISO | PD10 | 98 | |||

| 99 | PB0 | GTX0 | GMAC | PWMH0 | SPI0_SPCK | PD12 | 100 | |||

| 101 | PB7 | GRX3 | RK1 | SPI0_MOSI | PD11 | 102 | ||||

| 103 | PB13 | GRXER | PWML3 | PWMH3|GRXDV | GMAC:INTRP | PB12 | 104 | |||

| 105 | PB17 | GMDIO | GCOL | CAN0 | CANTX1 | PB15 | 106 | |||

| 107 | PB11 | GRXCK | RD1 | GCRS | CANRX1 | PB14 | 108 | |||

| 109 | PB18 | G125CK | GTX7 | MCI1 | MCI1_DA2 | PB22 | 110 | |||

| 111 | PB1 | GTX1 | PWML0 | GRX5 | MCI1_CK | PB24 | 112 | |||

| 113 | PB4 | GRX0 | PWMH1 | GTX5 | MCI1_DA0 | PB20 | 114 | |||

| 115 | PB3 | GTX3 | TF1 | GTX6 | MCI1_DA1 | PB21 | 116 | |||

| 117 | PB8 | GTXCK | PWMH2 | GTX4 | MCI1_CDA | PB19 | 118 | |||

| 119 | PB9 | GTXEN | PWML2 | GRX4 | MCI1_DA3 | PB23 | 120 | |||

| 121 | PB2 | GTX2 | TK1 | G125CKO | USART1 | RTS1 | PB27 | 122 | ||

| 123 | PB6 | GRX2 | TD1 | RXD1 | PB28 | 124 | ||||

| 125 | PB5 | GRX1 | PWML1 | TXD1 | PB29 | 126 | ||||

| 127 | PB16 | GMDC | GRX7 | CTS1 | PB26 | 128 | ||||

| 129 | PB25 | SCK1|GRX6 | RF1|GTXER | EMAC:INT_N | PB10 | 130 | ||||

| 131 | BMS | DIBN | 132 | |||||||

| 133 | NRST | DIBP | 134 | |||||||

| 135 | TDI | DEBUG | DTXD | PB31 | 136 | |||||

| 137 | JTAGSEL | DRXD | PB30 | 138 | ||||||

| 139 | TCK | SWCLK | SPI0_NPCS3|RTS0 | SSC0:IRQ | PD16 | 140 | ||||

| 141 | TMS | SWDIO | GND_POWER | 142 | ||||||

| 143 | TDO | USBA | DHSDP | HHSDPA | 144 | |||||

| 145 | NTRST | DHSDM | HHSDMA | 146 | ||||||

| 147 | WKUP | USBB | HHSDPB | 148 | ||||||

| 149 | SHDN | HHSDMB | 150 | |||||||

| 151 | D7 | EBI:Dx | USBC | HHSDMC | 152 | |||||

| 153 | D6 | HHSDPC | 154 | |||||||

| 155 | D5 | LCDDAT23|TIOB2 | EBI | NCS2 | PE28 | 156 | ||||

| 157 | D4 | LCDDAT22|TIOA2 | NCS1 | PE27 | 158 | |||||

| 159 | D3 | USART2:CTS2 | A23 | PE23 | 160 | |||||

| 161 | D2 | USART2:RXD2 | A25 | PE25 | 162 | |||||

| 163 | D1 | USART2:TXD2 | NCS0 | PE26 | 164 | |||||

| 165 | D0 | A20 | PE20 | 166 | ||||||

| 167 | PE3 | A3 | EBI:Ax | GPIO:LED | USART2:RTS2 | A24 | PE24 | 168 | ||

| 169 | PE5 | A5 | TCLK2 | NWR1/NBS1 | PE29 | 170 | ||||

| 171 | PE6 | A6 | USART3:RXD3 | A18 | PE18 | 172 | ||||

| 173 | PE13 | A13 | USART3:TXD3 | A19 | PE19 | 174 | ||||

| 175 | PE15 | A15 | SCK3 | PWML1|IRQ | MMC1:VDD_EN | PE31 | 176 | |||

| 177 | PE8 | A8 | NWAIT | MMC1:CD | PE30 | 178 | ||||

| 179 | PE10 | A10 | GPIO:LED | EBI:Ax | A4 | PE4 | 180 | |||

| 181 | PE14 | A14 | GPIO:LED | A2 | PE2 | 182 | ||||

| 183 | PE16 | A16 | CTS3 | GPIO:LED | A1 | PE1 | 184 | |||

| 185 | PE0 | A0/NBS0 | A7 | PE7 | 186 | |||||

| 187 | PE11 | A11 | RTS3 | A17 | PE17 | 188 | ||||

| 189 | GND_POWER | A9 | PE9 | 190 | ||||||

| 191 | GND_POWER | A12 | PE12 | 192 | ||||||

| 193 | GND_POWER | VCC_3V3 | 194 | |||||||

| 195 | GND_POWER | VCC_3V3 | 196 | |||||||

| 197 | GND_POWER | VCC_3V3 | 198 | |||||||

| 199 | GND_POWER | VCC_3V3 | 200 | |||||||

| 说明1:“可复用的信号”栏中黄色背景表示在MYZR-SAMA5-EK200上实现的信号。 | ||||||||||

| 说明2:MYZR-SAMA5-CB200-D36引出的管脚主要有PA0~PA31、PB0~PB31、PC0~PC31、PD0~PD12、PD14~PD31、PE0~PE20、PE23~PE31。 | ||||||||||

SAMA5D3 MPU介绍

SAMA5关键亮点

高性能

SAMA5 系列是专为弥补 ARM Cortex-A5 内核在功率方面的不足而设计,包括的器件能以低至 150 mW 的功耗提供高达 945DMIPS 的处理能力。

- 1.58 DMIPS/MHz ARM Cortex-A5 内核

- 高达 600 MHz 的最大工作频率 (945DMIPS)

- 64 位内部总线架构、可提供高达 1600 MB/s 带宽的 32 位宽 DDR 控制器

- 用于高精度计算和快速数据处理的 Neon 和浮点运算单元 (FPU)

- ARM Cortex-A5 FPU 的性能是 ARM Cortex-A8 FPU 的三倍

- L2 缓存,用于提高整体系统性能

- 1.58 DMIPS/MHz ARM Cortex-A5 内核

低功耗

SAMA5 器件采用创新技术以降低所有模式下的功耗,并且可实现:

- 在激活所有外设的情况下,以低于 150mW 的功耗(在工作模式下)提供高达 536MHz 的工作频率

- 在运行 SRAM 和 寄存器保留的低功耗模式下,功耗低于 0.5mW 且唤醒时间短于 0.5ms。在运行RTC(实时时钟)的备份模式下功耗约为 1.2μA

- 电池供电系统的理想之选

- 在激活所有外设的情况下,以低于 150mW 的功耗(在工作模式下)提供高达 536MHz 的工作频率

连接性

SAMA5 器件嵌入了各种高级通信外设,因此是网桥和网关的理想之选。

- 支持 IEEE1588 的以太网 MAC 和千兆位以太网 MAC、双 CAN 端口

- 可配置为三个主机或两个主机及一个器件端口的三个高速 USB 端口

- 多个 SDIO/SD/MMC 端口、UART、SPI、TWI、软调制解调器、CMOS 图像传感器接口、ADC、32 位定时器等。有关更多详细信息,请参阅“器件概述”选项卡

- 支持 IEEE1588 的以太网 MAC 和千兆位以太网 MAC、双 CAN 端口

增强的用户界面

使用 SAMA5 MPU,可以创建当今应用所需的时尚、平稳的用户界面。

- 图形 LCD 控制器具有图像合成叠加和集成功能(如 α 混合、缩放、颜色转换和旋转)

- 720p 硬件视频解码器,用于加快支持当今主流视频标准的视频回放

- 电阻式触摸屏界面

- CMOS 图像传感器接口

- 图形 LCD 控制器具有图像合成叠加和集成功能(如 α 混合、缩放、颜色转换和旋转)

安全

SAMA5 系列包括防止克隆、确保真实性以及保护应用的通信和数据存储安全的功能。

- 安全引导

- 硬件加密引擎,如高级加密标准 (AES)/三重数据加密标准 (DES)、RSA (Rivest-Shamir-Adleman) 和 ECC(椭圆曲线加密)以及安全哈希算法 (SHA) 和真正的随机号码生成器 (TRNG)

- 通过外部 DDR 内存即时加密/解密代码

- 管脚篡改检测,以保护系统免受物理入侵

- 密钥和数据的安全存储

- ARM 信任区域,用于对系统、外设和内存资源进行分区,以将安全关键型软件与开放环境操作系统隔离

- 安全引导

安全性

SAMA5 系列具有的功能可轻松简便地实施如 IEC61508 等安全标准。

- 主晶体振荡器时钟具有故障检测器

- 上电复位

- 独立的看门狗定时器

- 寄存器写保护

- 内存管理单元 (MMU) 允许在内存内设置区域保护

- 基于 SHA 的 ICM(完整性检查监控器),用于验证内存内容的完整性

- Arm 信任区域

- 主晶体振荡器时钟具有故障检测器

低系统成本

SAMA5 凭借高度的系统集成,在实现最大灵活性的同时还减少了对其他昂贵组件的需求。

- 0.8mm 球间距封装简化了 PCB 设计并降低了成本

- 最低功耗方案,需要芯片离散的电源或低成本 PMIC

- 三个高速 USB 端口节省了外部集线器的成本

- DDR(双数据速率)内存线路上的阻抗控件节省了外部电阻器

- 嵌入式 RTC 节省了外部组件

- 集成的软调制解调器解决方案节省了外部调制解调器设备的成本

- 0.8mm 球间距封装简化了 PCB 设计并降低了成本

SAMA5D3特性

核心

- ARM Cortex-A5处理器与ARM v7-A Thumb2? 指令系统

- CPU频率最高可达536 MHz

- CPU频率最高可达536 MHz

- 32 KB数据高速缓存,32 KB指令高速缓存,虚拟内存系统架构(VMSA)

- 完全集成的MMU和浮点单元(VFPv4)

- ARM Cortex-A5处理器与ARM v7-A Thumb2? 指令系统

记忆

- 一个160 KB的内部ROM单周期访问,系统速度,嵌入式启动加载器:8位启动。

- NAND闪存、SDCard、eMMC、串行数据流?,选择

- 一个128 KB的内部SRAM,系统速度下的单周期访问。

- 高带宽32位多端口动态RAM控制器支持512 Mbyte 8 bank DDR2 / LPDDR / LPDDR2与数据路径加扰。

- 独立静态存储器控制器,具有数据通路加扰和SLC / MLC NAND支持,最高可达24位纠错码(PMECC)。

- 一个160 KB的内部ROM单周期访问,系统速度,嵌入式启动加载器:8位启动。

系统运行频率高达166 MHz

- 复位控制器,关断控制器,周期性间隔定时器,看门狗定时器和实时时钟。

- 引导模式选择选项,重命名命令。

- 内部低功耗32 kHz RC振荡器和快速12 MHz RC振荡器。

- 可选32768 Hz低功耗振荡器和12 MHz振荡器。

- 一个用于系统的400至1000 MHz PLL和一个480 MHz的PLL优化d用于USB高速。

- 39个DMA通道,包括两个8通道64位的中央DMA控制器。br>

- 64位高级中断控制器。

- 3个可编程的外部时钟信号。

- 可编程保险丝盒,带256个熔丝位,其中192个可供客户使用。

- 复位控制器,关断控制器,周期性间隔定时器,看门狗定时器和实时时钟。

低功耗管理

- 关闭控制器

- 电池备份寄存器

- 时钟脉冲发生器和电源管理控制器

- 非常慢的时钟操作模式,软件可编程的功率优化能力

- 关闭控制器

外围设备

- LCD TFT控制器具有叠加,Alpha混合,旋转,缩放和色彩空间转换

- ITU-R BT,601/656图像传感器接口

- 3个HS/FS/LS USB端口和芯片上的收发器。

- 一个设备控制器

- 一个带集成根集线器的主机控制器(3个下行端口)

- 一个设备控制器

- 支持IEEE1588的一个10/100/1000 Mbps千兆以太网MAC控制器(GMAC)

- 一个10/100 Mbps以太网MAC控制器(EMAC)

- 两个CAN控制器,带有8个邮箱,完全符合CAN 2.0 A部分和2.0 B部分

- Softmodem接口

- 三个高速存储卡主机(eMMC 4.3和SD 2.0)

- 两个主/从串行外设接口

- 两个同步串行控制器

- 三个双线接口,最高400 Kbit / s,支持I2C协议和SMBUS

- 四个USART,两个UART,一个DBGU

- 两个三通道32位定时器/计数器

- 一个4通道16位PWM控制器

- 一个具有电阻式触摸屏功能的12通道12位模数转换器

- LCD TFT控制器具有叠加,Alpha混合,旋转,缩放和色彩空间转换

安全

- 上电复位单元

- 独立看门狗

- 主晶振时钟故障检测

- 写保护寄存器

- SHA:支持安全散列算法(SHA1,SHA224,SHA 256,SHA384,SHA512)

- 内存管理单元

- 上电复位单元

保密

- TRNG:真正的随机数生成器

- 加密引擎

- AES:256位,192位,128位密钥算法,符合FIPS PUB 197规范

- TDES:双键或三键算法,符合FIPS PUB 46-3规范

- AES:256位,192位,128位密钥算法,符合FIPS PUB 197规范

- Atmel? 安全启动解决方案

- TRNG:真正的随机数生成器

I/O

- 五个32位并行输入/输出控制器

- 160 I/O

- 输入改变每个I/O线上的中断能力,可选施密特触发器输入

- 可单独编程的开漏,上拉和下拉电阻,同步输出,滤波

- 高速I/O的转换速率控制

- DDR I/O的阻抗控制

- 五个32位并行输入/输出控制器

程序包

- 324-ball LFBGA, 15 x 15 x 1.4 mm, 间距 0.8 mm

- 324-ball TFBGA, 12 x 12 x 1.2 mm, 间距 0.5 mm

- 324-ball LFBGA, 15 x 15 x 1.4 mm, 间距 0.8 mm

SAMA5D3 嵌入式特性

WDT

- 12位密钥保护可编程计数器

- 看门狗时钟独立于处理器时钟

- 为系统提供复位或中断信号

- 计数器可能在处理器处于调试状态或处于空闲模式时停止

- 看门狗时钟独立于处理器时钟

RTC

- 超低功耗

- 完全异步设计

- 格里高利历直到2099年

- 可编程周期中断

- 安全/安全功能:

- 有效的时间和日期计划检查

- 有效的时间和日期计划检查

- 超低功耗

PIO

- 最多32个可编程I/O线

- 可通过置位/清除寄存器完全编程

- 每个I/O线路复用四个外设功能

- 对于每个I/O线(是分配给外设还是用作通用I/O)

- 输入更改中断

- 可编程毛刺滤波器

- 可编程去噪滤波器

- 多驱动器选项可实现开漏式驱动

- 每个I/O线上的可编程上拉电阻

- 引脚数据状态寄存器,随时提供引脚电平的可见性

- 可编程事件的附加中断模式:上升沿,下降沿,低电平或高电平

- 通过连接的外围设备锁定配置

- 输入更改中断

- 同步输出,在单次写入中提供几个I/O线的置位和清除

- 寄存器写保护

- 可编程施密特触发器输入

- 可编程I/O驱动器

- 最多32个可编程I/O线

LCDC

- 双AHB主接口

- 支持单扫描有源TFT显示器

- 通过空间抖动单元支持12,16,18和24位输出模式

- 支持异步输出模式(在合成时)

- 每像素1,2,4,8位(托盘化)

- 12,16,18,19,24,25和32位/像素(非托盘化)

- 支持一个基本层(背景)

- 支持两个叠加层Windows

- 支持一个高端覆盖(HEO)窗口

- 支持一个硬件光标,固定或自由尺寸

- 硬件光标固定大小在以下模式:32x32,64x64和128x128

- Little Endian Memory Organization

- 可编程定时引擎,带整数时钟分频器

- 数据的可编程极性,线同步和帧同步。

- 显示尺寸最大为2048x2048,或视频格式最高为720p

- 颜色查找表,最多256个条目和预定义的8位Alpha

- 可编程负和正行跨步所有图层

- 可编程负像素和正像素跨越所有Overlay1,Overlay2和HEO图层

- 高端覆盖支持4:2:0平面模式和半平面模式

- 高端覆盖支持4:2:2平面模式,半平面模式和Packed

- 高端覆盖包括色度上采样单元

- 具有边缘插值和独立非整数比的水平和垂直重定标单元

- 支持隐藏层删除。

- 集成完全可编程的色彩空间转换

- Overlay1,Overlay2和High End Overlay集成旋转引擎:90,180,270

- Blender功能支持任意8位Alpha值和色度键控

- DMA用户界面使用链接列表结构和添加到队列结构

- 双AHB主接口

ISI

- ITU-R BT,601/656 8位模式外部接口支持

- 支持最高12位灰度CMOS传感器

- 支持ITU-R BT.656-4 SAV和EAV同步

- 垂直和水平分辨率高达2048 * 2048

- 预览路径

- 灰度模式下最高可达2048 * 2048

- RGB模式下最高640 * 480

- 灰度模式下最高可达2048 * 2048

- Codec Path上的32字节FIFO

- 预览路径上的32字节FIFO

- 支持YCbCr 4:2:2 Formats

的打包数据格式 - 预览缩放器以生成更小的图像

- 可编程帧捕获率

- 支持LCD预览的VGA,QVGA,CIF,QCIF格式

- 自定义格式,水平和垂直预览大小为16的倍数也支持LCD预览<

- ITU-R BT,601/656 8位模式外部接口支持

UDPHS

- 1设备高速

- 1主机和设备之间共享的UTMI收发器

- USB v2.0高速兼容,480Mbit/s

- 16个端点,最多1024个字节

- 用于端点的嵌入式双端口RAM

- 暂停/恢复逻辑(UTMI的命令)

- 最多三个内存组用于端点(不适用于控制端点)

- 8 KB的DPRAM

- 1设备高速

UHPHS

- 符合增强型HCI Rev 1.0规范

- 符合USB V2.0高速

- 支持高速480 Mbps

- 符合USB V2.0高速

- 符合OpenHCI Rev 1.0规范

- 符合USB V2.0全速和低速规格

- 支持低速1.5 Mbps和全速12 Mbps USB设备

- 符合USB V2.0全速和低速规格

- Root Hub集成了3个下行USB HS端口

- 嵌入式USB收发器

- 支持电源管理

- 主机(A和B)高速(EHCI),端口A与UDPHS共享

- 符合增强型HCI Rev 1.0规范

GMAC

- 与IEEE标准802.3兼容

- 10,100和1000 Mbps操作

- 在所有支持的操作速度下完全和半双工操作

- RMON / MIB的统计计数器寄存器

- 物理层的MII / GMII / RGMII接口

- 集成物理编码

- 直接内存访问(DMA)接口到外部存储器

- DMA的可编程突发长度和字节序

- 中断生成以指示接收和发送完成,或错误

- 在传输帧上自动填充和循环冗余校验(CRC)生成

- 半双工模式下帧扩展和帧突发1000 Mbps

- 自动丢弃收到错误的帧

- 接收和传输IP,TCP和UDP校验和卸载。支持IPv4和IPv6数据包类型

- 地址检查逻辑,用于四个特定的48位地址,四种类型ID,混杂模式,

的哈希匹配 - 单播和多播目标地址和局域网唤醒

- 物理层管理的管理数据输入/输出(MDIO)接口

- 支持最大10240字节的巨型帧

- 全双工流量控制,识别传入暂停帧和硬件生成传输暂停

- 帧点击

- 通过强制传入帧上的冲突来实现半双工流量控制

- 支持802.1Q VLAN标记,识别传入VLAN和优先级标记帧

- 支持基于802.1Qbb优先级的流量控制

- 可编程数据包间隙(IPG)拉伸

- IEEE 1588 PTP帧的识别

- IEEE 1588时间戳单元(TSU)

- 支持802.1AS定时和同步

EMAC

- 支持物理层的RMII接口

- 与IEEE标准802.3兼容

- 10和100 Mbit / s操作

- 全双工和半双工操作

- 统计计数器寄存器

- 中断生成到信号接收和发送完成

- DMA主接收和发送通道

- 发送和接收FIFO

- 传输帧上的自动填充和CRC生成

- 自动丢弃因错??误而收到的帧

- 地址检查逻辑支持最多四个特定的48位地址

- 支持混杂模式,其中所有有效接收帧都复制到内存

- 单播和多播目标地址的哈希匹配

- 通过MDIO接口进行物理层管理

- 通过强制进入帧的冲突实现半双工流控制

- 具有识别输入暂停帧的全双工流量控制

- 支持802.1Q VLAN标记,识别入局VLAN和优先级标记帧

- 每个接收和发送帧多个缓冲区

- 局域网唤醒支持

- Jumbo帧最多支持10240字节

- 支持物理层的RMII接口

HSMCI

- 兼容多媒体卡规范版本4.3

- 兼容SD存储卡规范版本2.0

- 兼容SDIO规范版本2.0

- 与CE-ATA规范1.1兼容

- 卡时钟速率高达主时钟除以2

- 引导操作模式支持

- 高速模式支持

- 嵌入式电源管理,在不使用时降低时钟速率

- 支持1个多路复用插槽

- 每个插槽用于高速多媒体卡总线(最多30个卡)或SD存储卡

- 每个插槽用于高速多媒体卡总线(最多30个卡)或SD存储卡

- 支持流,块和多块数据读写

- 支持连接到DMA控制器(DMAC)

- 最大限度地减少大型缓冲区传输的处理器干预

- 最大限度地减少大型缓冲区传输的处理器干预

- 内置FIFO(16至256字节),大内存孔径支持增量访问

- 支持CE-ATA完成信号禁用命令

- 防止配置寄存器的即时修改意外

- 兼容多媒体卡规范版本4.3

SPI

- 支持与串行外部设备通信

- 主模式可以将SPCK驱动到外设时钟(以最大总线时钟除以2为限)

- 从模式在SPCK上运行,与核心和总线时钟异步

- 具有外部解码器支持的四个芯片选择允许与多达15个外设进行通信

- 串行存储器,如DataFlash和3线EEPROM

- 串行外设,如ADC,DAC,LCD控制器,CAN控制器和传感器

- 外部协处理器

- 主或从串行外设总线接口

- 每片8位至16位可编程数据长度选择

- 每个芯片的可编程相位和极性选择

- 每个芯片SPI时钟选择之前的可连续传输和延迟之间的可编程传输延迟

- 芯片选择之间的可编程延迟

- 可选模式故障检测

- 每片8位至16位可编程数据长度选择

- 与DMA通道功能的连接优化数据传输

- 接收器的一个通道,发送器的一个通道

- 接收器的一个通道,发送器的一个通道

- 支持与串行外部设备通信

TWI

- 3 TWIs

- 兼容Atmel双线接口串行存储器和I2C兼容设备

- 从属地址的一个,两个或三个字节

- 顺序读写操作

- Master,Multi-master和Slave Mode Operation

- 比特率:高达400 Kbit / s

- 从属模式支持的一般呼叫

- 主模式支持的SMBUS快速命令

- 与DMA控制器(DMA)通道功能的连接优化数据传输

- 3 TWIs

SSC

- 提供用于音频和电信应用的串行同步通信链路

- 包含独立接收器和发送器以及公共时钟分频器

- 与DMA控制器(DMAC)接口以减少处理器开销

- 提供可配置的帧同步和数据长度

- 接收器和发射器可以编程为自动启动或检测到不同事件

- 帧同步信号

- 接收器和发送器包括数据信号,时钟信号和帧同步信号

- 提供用于音频和电信应用的串行同步通信链路

DBGU

- 系统外设,以促进Atmel的调试?基于ARM?的系统

- 由四个函数组成

- 双引脚UART

- 调试通信通道(DCC)支持

- 芯片ID寄存器

- ICE访问预防

- 双引脚UART

- 双引脚UART

- 已实现的功能是USART兼容的

- 具有通用可编程波特率发生器的独立接收器和发送器

- 偶数,奇数,标记或空间奇偶生成

- 奇偶校验,成帧和溢出错误检测

- 自动回声,本地环回和远程环回信道模式

- 中断生成

- 支持连接到接收器和发送器的两个DMA通道

- 已实现的功能是USART兼容的

- 调试通信渠道支持

- 提供来自ARM处理器的COMMRX和COMM TX信号的可见性

- 中断生成

- 芯片ID注册

- 设备版本的识别,嵌入式存储器的大小,外围设备集

- 设备版本的识别,嵌入式存储器的大小,外围设备集

- ICE访问预防

- 使软件能够通过ARM处理器的ICE防止系统访问

- 通过断言ARM处理器的ICE的NTRST线进行预防

- 系统外设,以促进Atmel的调试?基于ARM?的系统

UART

- 双引脚UART

- 具有通用可编程波特率发生器的独立接收器和发送器

- 偶数,奇数,标记或空间奇偶生成

- 奇偶校验,成帧和溢出错误检测

- 自动回声,本地环回和远程环回信道模式

- 中断生成

- 支持连接到接收器和发送器的两个DMA通道

- 具有通用可编程波特率发生器的独立接收器和发送器

- 双引脚UART

USART

- 可编程波特率发生器

- 5至9位全双工同步或异步串行通信

- 异步模式下的1个,1.5个或2个停止位或同步模式下的1个或2个停止位

- 奇偶校验生成和错误检测

- 帧错误检测,溢出错误检测

- MSB-或LSB-first

- 可选的中断生成和检测

- 8或16过采样接收器频率

- 可选硬件握手RTS-CTS

- 接收器超时和发射器Timeguard

- 带地址生成和检测的可选多点模式

- 带驱动器控制信号的RS485

- ISO7816,T = 0或T = 1与智能卡接口的协议

- NACK处理,具有重复和迭代限制的错误计数器

- IrDA调制和解调

- 通信速率高达115.2 Kbps

- NACK处理,具有重复和迭代限制的错误计数器

- SPI模式

- 主人或奴隶

- 串行时钟可编程相位和极性

- SPI串行时钟(SCK)频率高达内部时钟频率MCK / 6

- 主人或奴隶

- 测试模式

- 远程环回,本地环回,自动回声

- 远程环回,本地环回,自动回声

- 支持连接:

- 两个DMA控制器通道(DMAC)

- 两个DMA控制器通道(DMAC)

- 提供无处理器干预的缓冲区传输

- 可编程波特率发生器

CAN

- 完全符合CAN 2.0 A部分和2.0 B部分

- 比特率高达1 Mbit / s

- 8个具有以下属性的面向对象的邮箱:

- CAN规范2.0 A部分或2.0 B部分可编程为每个消息

- 对象可在接收(具有覆盖或不覆盖)或发送模式中配置

- 为每个邮箱定义独立的29位标识符和掩码

- 每个邮箱数据对象的32位数据寄存器访问

- 在接收和发送消息时使用16位时间戳

- ID屏蔽位域的硬件级联,以加快系列ID处理

- CAN规范2.0 A部分或2.0 B部分可编程为每个消息

- 用于时间戳和网络同步的16位内部定时器

- 可编程接收缓冲区长度最多8个邮箱对象

- 传输邮箱之间的优先级管理

- Autobaud和Listening Mode

- 低功耗模式和可编程唤醒总线活动或应用程序

- 数据,远程,错误和过载帧处理

- 写保护寄存器

- 完全符合CAN 2.0 A部分和2.0 B部分

PWM

- 频道点击

- 通用时钟发生器提供十三种不同的时钟

- 提供十一个时钟的模数计数器

- 两个独立的线性分频器工作模数n计数器输出

- 提供十一个时钟的模数计数器

- 独立频道

- 每个通道独立的16位计数器

- 每个通道的12位死区发生器(也称为死区或非重叠时间)的独立互补输出

- 每个通道的独立启用禁用命令

- 每个通道的独立时钟选择

- 每个频道的独立时段,占空比和死区时间

- 每个通道的周期,占空比和死区的独立双缓冲

- 独立可编程选择每个通道的输出波形极性

- 每个通道的独立可编程中心或左对齐输出波形

- 每个通道的独立输出覆盖

- 每个通道的独立中断,在每个周期进行左对齐或中心对齐配置

- 每个通道独立的16位计数器

- 2步进电机控制的2位灰色上/下通道

- 同步信道模式

- 同步通道共享同一个计数器

- 在可编程周期数后更新同步通道寄存器的模式

- 同步通道共享同一个计数器

- 2个用于同步ADC转换的独立事件行

- 事件线的可编程延迟,以延迟ADC测量

- 事件线的可编程延迟,以延迟ADC测量

- 8个用于在事件线上产生中断,脉冲的比较单元

- 1可编程故障/中断输入提供PWM输出的异步保护

- 4用户通过PIO输入驱动

- 当晶体振荡器时钟失效时PMC驱动

- ADC控制器通过可配置比较功能驱动

- 4用户通过PIO输入驱动

- 写保护寄存器

ADC

- 12位分辨率

- 1 MHz转换率

- 宽范围电源操作

- 可选择单端或差分输入电压

- 可编程增益,用于最大满量程输入范围0 - VDD

- 电阻式4线和5线触摸屏控制器

- 4线屏幕的位置和压力??测量

- 5线屏幕的位置测量

- 噪声滤波最多8个平均值的平均值

- 4线屏幕的位置和压力??测量

- 可编程笔检测灵敏度

- 集成多路复用器,提供多达12个独立模拟输入

- 单个启用和禁用每个通道

- 硬件或软件触发器

- 外部触发引脚

- 定时器计数器输出(对应的TIOA触发器)

- 内部触发计数器

- 笔触点检测触发

- PWM事件线

- 外部触发引脚

- PWM故障输入驱动

- DMA支持

- ADC时序配置的可能性

- 两种睡眠模式和转换序列器

- 在所有启用的通道转换后,触发和返回睡眠模式下的自动唤醒

- 自定义频道序列的可能性

- 在所有启用的通道转换后,触发和返回睡眠模式下的自动唤醒

- 快速唤醒时间响应的待机模式

- 断电能力

- 断电能力

- 转换值的自动窗口比较

- 写保护寄存器

- 写保护寄存器

- 12位分辨率