MYZR-RK3399-MB314 硬件介绍

目录

接口功能

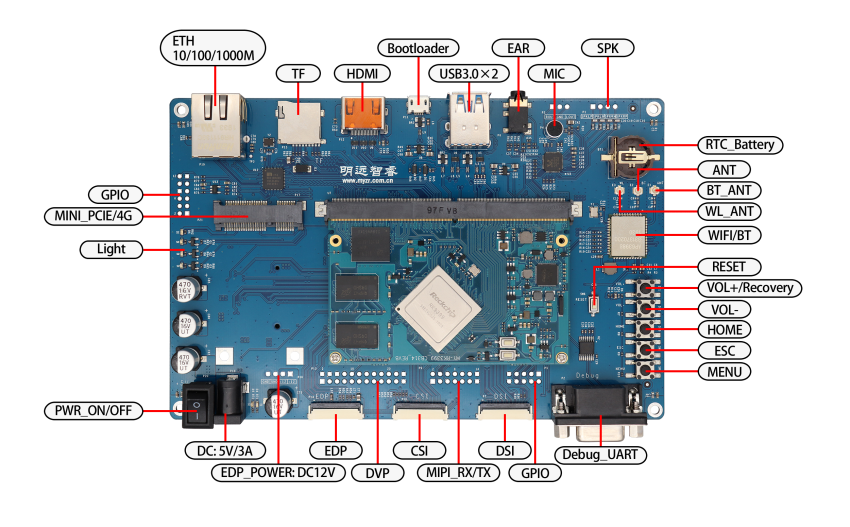

'MYZR-RK3399-MB314 正面图

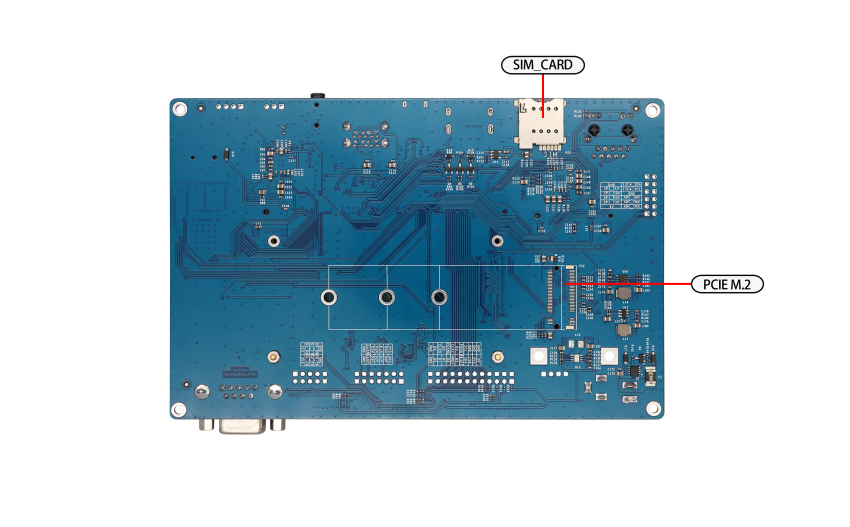

'MYZR-RK3399-MB314 背面图

电源接口

MYZR-RK3399_CB314 模块电源接口定义如下表所示:

| 管脚号 | 管脚定义 | I/O属性 | 功能描述 |

| P1 ~ P9 | VCC_SYS | PI | 模块工作电源输入,5V/3A |

| P10 | VCC_RTC | PI | RTC 实时时钟电源输入,3.3V供电 |

| S10~S12 | VCC3V3_SYS | PO | 3.3V输出,峰值可达2A |

| S13~S15 | VCC_1V8 | PO | 1.8V输出,峰值可达 1A |

| S16、S17 | VCCA3V0_CODEC0 | PO | 3.0V输出,峰值可达 300mA |

| S18、S19 | VCCA1V8_CODEC0 | PO | 1.8V输出,峰值可达 300mA |

| S20 | VCC1V8_DVP | PO | 1.8V输出,峰值可达 150mA |

| P11、P23、P31、P42、P58、P74、P81、P89、P100、P109、P119、P133、P140、P147、P154~P156、

S1~S9、S21、S22、S26、S47、S50、S53、S56、S59、S62、S65、S76、S79、S82、S85、S88、S91、 S94、S97、S100、S103、S106、S108、S110、S112、S115、S118、S121、S124、S127、S130、S133、 S136、S137、S140、S143、S146、S149、S152、S155、S158 |

GND | - | 地 |

MYZR-RK3399_CB314 模块使用 VCC_SYS 供电,为保证模块能正常运行,供电电源电压不低于4.6V,不超过 5.5V,供电电流不低于 3A。建议在模块供电端口加一个大于 470uF 的电容。

多媒体接口

EDP接口

MYZR-RK3399_CB314 模块eDP接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S144 | EDP_TX3P | D30 | EDP_TX3P | O | eDP data lane3 positive output |

| S145 | EDP_TX3N | D31 | EDP_TX3N | O | eDP data lane3 negative output |

| S147 | EDP_TX2P | C30 | EDP_TX2P | O | eDP data lane2 positive output |

| S148 | EDP_TX2N | C31 | EDP_TX2N | O | eDP data lane2 negative output |

| S150 | EDP_TX1P | B30 | EDP_TX1P | O | eDP data lane1 positive output |

| S151 | EDP_TX1N | A30 | EDP_TX1N | O | eDP data lane1 negative output |

| S153 | EDP_TX0P | B29 | EDP_TX0P | O | eDP data lane0 positive output |

| S154 | EDP_TX0N | A29 | EDP_TX0N | O | eDP data lane0 negative output |

| S156 | EDA_AUXP | B28 | EDPAUXP | I/O | eDP CH-AUX positive differential output |

| S157 | EDA_AUXN | A28 | EDPAUXN | I/O | eDP CH-AUX negative differential output |

eDP 走线请注意:

- eDP 信号的参考时钟建在数据中,在接收端还原出时钟信号,所以四组数据差分线对组间不做等长,只需做组内等长处理;

- 为抑制电磁辐射,eDP信号建议PCB内层走线,并保证走线参考面是一个连续完整的参考面,不被分割,否则会造成差分线阻抗的不连续性并引入外部噪声对的影响。如在PCB表层走线,请注意用地线做包地处理;差分对之间不需要伴随地走线;

eDP走线要求如表:

| 参数 | 要求 |

| Trace Impedance | 100Ω ±10% differential |

| Max intra-pair skew | < 4 ps |

| Max trace length on carrier board | < 6 inch |

| Minimum pair to pair spacing | > 3 times the width of the trace.Try to increase Spacing between pairs whenever it is possible. |

| AC coupling capacitors | 100nF ±20%, discrete 0201 package preferable |

| The minimum spacing between EDP and other Signals | At least 3 times the width of EDP trace. |

| Maximum allowed via | 4 |

HDMI接口

MYZR-RK3399_CB314 模块HDMI接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S48 | I2C3_SDA_3V3 | AG6 | GPIO4_C0/I2C3_SDA/UART2B_RX_u | IO | I2C data line for HDMI |

| S49 | I2C3_SCL_3V3 | AL2 | GPIO4_C1/I2C3_SCL/UART2B_TX_u | IO | I2C clock line for HDMI |

| S66 | HDMI_CEC | AD7 | GPIO4_C7/HDMI_CECINOUT/EDP_HOTPLUG_u | IO | HDMI CEC signal |

| S67 | HDMI_TXCP | AK16 | HDMI_TXCP | O | HDMI positive TMDS differential line driver clock output |

| S68 | HDMI_TXCN | AL16 | HDMI_TXCN | O | HDMI negative TMDS differential line driver clock output |

| S69 | HDMI_TX0P | AK17 | HDMI_TX0P | O | HDMI positive TMDS differential line0 driver data output |

| S70 | HDMI_TX0N | AL17 | HDMI_TX0N | O | HDMI negative TMDS differential line0 driver data output |

| S71 | HDMI_TX1P | AK18 | HDMI_TX1P | O | HDMI positive TMDS differential line1 driver data output |

| S72 | HDMI_TX1N | AL18 | HDMI_TX1N | O | HDMI negative TMDS differential line1 driver data output |

| S73 | HDMI_TX2P | AK19 | HDMI_TX2P | O | HDMI positive TMDS differential line2 driver data output |

| S74 | HDMI_TX2N | AL19 | HDMI_TX2N | O | HDMI negative TMDS differential line2 driver data output |

| S75 | PORT_HPD | AE15 | HDMI_HPD | IO | HDMI hot plug detect signal |

HDMI走线请注意:

- HDMI TX信号的参考时钟为HDMI TXC,所以包括时钟在内的四组差分对都需要做等长处理;

- HDMI信号需要保证走线参考面是一个连续完整的参考面,不被分割, 否则会造成差分线阻抗的不连续性并引入外部噪声对的影响。在PCB表层走线请注意用地线做整组包地处理; 差分对之间不需要伴随地走线;

- HDMI信号可以直接顺序扇出到HDMI连接座,走线中应该尽可能的减少换层过孔,过孔会造成线路阻抗的不连续;如果因为模具结构无法避免换层,建议将换层的阻抗变化控制在10%以内,并在每对换层的差分对旁边就近安排一个GND过孔用于信号回流路径的换层;

- ESD器件靠近HDMI连接座放置;

- 使用带屏蔽层的HDMI线缆,能有效改善EMI问题;

HDMI走线要求如表:

| 参数 | 要求 |

| Trace Impedance | 100Ω ±10% |

| Max intra-pair skew | < 4ps |

| Max trace length skew between clock and data pairs | < 80ps |

| Max trace length on carrier board | < 9.8 inchs |

| Minimum pair to pair spacing | > 3 times the width of the trace.Try to increase Spacing between pairs whenever it is possible |

| The minimum spacing between HDMI and other Signals | At least 3 times the width of HDMI trace |

| Maximum allowed via | 4 |

MIPI接口

MYZR-RK3399_CB314 模块MIPI接口定义如下表所示:

- MIPI DSI接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S51 | MIPI_TX0_D3N | AH9 | MIPI_TX0_D3N | IO | MIPI DSI negative differential data line3 transceiver output |

| S52 | MIPI_TX0_D3P | AG9 | MIPI_TX0_D3P | IO | MIPI DSI positive differential data line3 transceiver output |

| S54 | MIPI_TX0_D2N | AH11 | MIPI_TX0_D2N | IO | MIPI DSI negative differential data line2 transceiver output |

| S55 | MIPI_TX0_D2P | AG11 | MIPI_TX0_D2P | IO | MIPI DSI positive differential data line2 transceiver output |

| S57 | MIPI_TX0_CLKN | AH12 | MIPI_TX0_CLKN | IO | MIPI DSI negative differential clock line transceiver output |

| S58 | MIPI_TX0_CLKP | AG12 | MIPI_TX0_CLKP | IO | MIPI DSI positive differential clock line transceiver output |

| S60 | MIPI_TX0_D1N | AH14 | MIPI_TX0_D1N | IO | MIPI DSI negative differential data line1 transceiver output |

| S61 | MIPI_TX0_D1P | AG14 | MIPI_TX0_D1P | IO | MIPI DSI positive differential data line1 transceiver output |

| S63 | MIPI_TX0_D0N | AH15 | MIPI_TX0_D0N | IO | MIPI DSI negative differential data line0 transceiver output |

| S64 | MIPI_TX0_D0P | AG15 | MIPI_TX0_D0P | IO | MIPI DSI positive differential data line0 transceiver output |

- MIPI CSI/DSI接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S77 | MIPI_TX1/RX1_D1N | AL7 | MIPI_TX1/RX1_D1N | IO | MIPI CSI/DSI negative differential data line1 transceiver output |

| S78 | MIPI_TX1/RX1_D1P | AK7 | MIPI_TX1/RX1_D1P | IO | MIPI CSI/DSI positive differential data line1 transceiver output |

| S80 | MIPI_TX1/RX1_D0N | AL6 | MIPI_TX1/RX1_D0N | IO | MIPI CSI/DSI negative differential data line0 transceiver output |

| S81 | MIPI_TX1/RX1_D0P | AK6 | MIPI_TX1/RX1_D0P | IO | MIPI CSI/DSI positive differential data line0 transceiver output |

| S83 | MIPI_TX1/RX1_D2N | AL9 | MIPI_TX1/RX1_D2N | IO | MIPI CSI/DSI negative differential data line2 transceiver output |

| S84 | MIPI_TX1/RX1_D2P | AK9 | MIPI_TX1/RX1_D2P | IO | MIPI CSI/DSI positive differential data line2 transceiver output |

| S86 | MIPI_TX1/RX1_CLKP | AK8 | MIPI_TX1/RX1_CLKP | IO | MIPI CSI/DSI negative differential clock line transceiver output |

| S87 | MIPI_TX1/RX1_CLKN | AL8 | MIPI_TX1/RX1_CLKN | IO | MIPI CSI/DSI positive differential clock line transceiver output |

| S89 | MIPI_TX1/RX1_D3P | AK10 | MIPI_TX1/RX1_D3P | IO | MIPI CSI/DSI negative differential data line3 transceiver output |

| S90 | MIPI_TX1/RX1_D3N | AL10 | MIPI_TX1/RX1_D3N | IO | MIPI CSI/DSI positive differential data line3 transceiver output |

- MIPI CSI接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S92 | MIPI_RX0_D0P | AK15 | MIPI_RX0_D0P | IO | MIPI CSI positive differential data line0 transceiver output |

| S93 | MIPI_RX0_D0N | AL15 | MIPI_RX0_D0N | IO | MIPI CSI negative differential data line0 transceiver output |

| S95 | MIPI_RX0_D1P | AK14 | MIPI_RX0_D1P | IO | MIPI CSI positive differential data line1 transceiver output |

| S96 | MIPI_RX0_D1N | AL14 | MIPI_RX0_D1N | IO | MIPI CSI negative differential data line1 transceiver output |

| S98 | MIPI_RX0_CLKP | AK13 | MIPI_RX0_CLKP | IO | MIPI DSI positive differential clock line transceiver output |

| S99 | MIPI_RX0_CLKN | AL13 | MIPI_RX0_CLKN | IO | MIPI DSI negative differential clock line transceiver output |

| S101 | MIPI_RX0_D2P | AK12 | MIPI_RX0_D2P | IO | MIPI CSI positive differential data line2 transceiver output |

| S102 | MIPI_RX0_D2N | AL12 | MIPI_RX0_D2N | IO | MIPI CSI negative differential data line2 transceiver output |

| S104 | MIPI_RX0_D3P | AK11 | MIPI_RX0_D3P | IO | MIPI CSI positive differential data line3 transceiver output |

| S105 | MIPI_RX0_D3N | AL11 | MIPI_RX0_D3N | IO | MIPI CSI negative differential data line3 transceiver output |

MIPI DSI:

- 单MIPI工作模式下,必须使用MIPI_DSI0,即MIPI_TX0这组; MIPI-DSI1不能被单独使用;

- 双MIPI工作模式下,MIPI_TX0和MIPI_TX1/RX1通道可以根据布局以及走线需要,整组调换使用;

MIPI CSI:

- RK3399有两组MIPI-CSI输入,均内置ISP处理器,在双MIPI输入的时候可以同时使用。

MIPI 走线请注意:

- 为抑制电磁辐射, MIPI信号建议PCB内层走线,并保证走线参考面是一个连续完整的参考面,不被分割, 否则会造成差分线阻抗的不连续性并引入外部噪声对的影响。如在PCB表层走线,请注意用地线做包地处理; 差分对之间不需要伴随地走线;

- MIPI信号在设置走线的延时时,请尽量靠近RK3399端;

MIPI 走线要求如表:

| 参数 | 要求 |

| Trace Impedance | 100Ω ±10% differential |

| Max intra-pair skew | < 4ps |

| Max trace length skew between clock and data pairs | < 7ps |

| Max trace length | < 7.2inch |

| Maximum allowed via | Minimize the number of via in each lane |

| Minimum pair to pair spacing | > 3 times the width of the trace.Try to increase Spacing between pairs whenever it is possible. |

| The minimum spacing between Mipi and other Signals | At least 3 times the width of Mipi trace. |

CIF接口

MYZR-RK3399_CB314 模块CIF接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P120 | CIF_D4 | H29 | GPIO2_A4/VOP_D4/CIF_D4_d | I | Camera interface input pixel data4 |

| P121 | CIF_D6 | H27 | GPIO2_A6/VOP_D6/CIF_D6_d | I | Camera interface input pixel data6 |

| P122 | CIF_CLKO | H31 | GPIO2_B3/SPI2_CLK/VOP_DEN/CIF_CLKOUTA_u | O | Camera interface output work clock |

| P123 | CIF_D1 | H25 | GPIO2_A1/VOP_D1/CIF_D1/I2C2_SCL_u | I | Camera interface input pixel data1 |

| P124 | CIF_D0 | G31 | GPIO2_A0/VOP_D0/CIF_D0/I2C2_SDA_u | I | Camera interface input pixel data0 |

| P125 | CIF_D7 | G30 | GPIO2_A7/VOP_D7/CIF_D7/I2C7_SDA_u | I | Camera interface input pixel data7 |

| P126 | DVP_PDN0_H | F31 | GPIO2_B4/SPI2_CSn0_u | IO | |

| P127 | CIF_VSYNC | H28 | GPIO2_B0/VOP_CLK/CIF_VSYNC/I2C7_SCL_u | I | Camera interface vertical sync signal |

| P128 | CIF_D2 | H30 | GPIO2_A2/VOP_D2/CIF_D2_d | I | Camera interface input pixel data2 |

| P129 | CIF_CLKI | H24 | GPIO2_B2/SPI2_TXD/CIF_CLKIN/I2C6_SCL_u | I | Camera interface input pixel clock |

| P130 | CIF_HREF | F30 | GPIO2_B1/SPI2_RXD/CIF_HREF/I2C6_SDA_u | I | Camera interface horizontial sync signal |

| P131 | CIF_D3 | F28 | GPIO2_A3/VOP_D3/CIF_D3_d | I | Camera interface input pixel data3 |

| P132 | CIF_D5 | F29 | GPIO2_A5/VOP_D5/CIF_D5_d | I | Camera interface input pixel data5 |

I2S/PCM接口

MYZR-RK3399_CB314 模块I2S/PCM接口定义如下表所示:

- I2S/PCM接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P12 | I2S_CLK | AC7 | GPIO4_A0/I2S_CLK_d | IO | I2S/PCM clock source, shared by I2S0 and I2S1 |

- I2S0/PCM0接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P13 | I2S0_SDI1 | AE5 | GPIO3_D4/I2S0_SDI1SDO3_d | IO | I2S/PCM serial data input[1] or output [3] |

| P14 | I2S0_SCLK | AG3 | GPIO3_D0/I2S0_SCLK_d | IO | I2S/PCM serial clock |

| P15 | I2S0_LRCK_RX | AF4 | GPIO3_D1/I2S0_LRCK_RX_d | IO | I2S/PCM left & right channel signal for receiving serial data,synchronous left & right channel

in I2S mode and the beginning of a group of left & right channels in PCM mode |

| P16 | I2S0_LRCK_TX | AJ2 | GPIO3_D2/I2S0_LRCK_TX_d | IO | I2S/PCM left & right channel signal for transmitting serial data, synchronous left & right channel

in I2S mode and the beginning of a group of left & right channels in PCM mode |

| P17 | I2S0_SDI0 | Y7 | GPIO3_D3/I2S0_SDI0_d | IO | I2S/PCM serial data input[0] |

| P18 | I2S0_SDO2 | AA6 | GPIO3_D5/I2S0_SDI2SDO2_d | IO | I2S/PCM serial data input [2] or output [2] |

| P19 | I2S0_SDO1 | AH2 | GPIO3_D6/I2S0_SDI3SDO1_d | IO | I2S/PCM serial data input [3] or output [1] |

| P20 | I2S0_SDO0 | AH1 | GPIO3_D7/I2S0_SDO0_d | IO | I2S/PCM serial data output [0] |

- I2S1/PCM1接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P24 | I2S1_SCLK_BT_PCM | AF3 | GPIO4_A3/I2S1_SCLK_d | IO | I2S/PCM serial clock |

| P25 | I2S1_LRCK_RX_BT_PCM | AA7 | GPIO4_A4/I2S1_LRCK_RX_d | IO | I2S/PCM left & right channel signal for receiving serial data,synchronous left & right channel

in I2S mode and the beginning of a group of left & right channels in PCM mode |

| P26 | I2S1_LRCK_TX_BT_PCM | AJ1 | GPIO4_A5/I2S1_LRCK_TX_d | IO | I2S/PCM left & right channel signal for transmitting serial data, synchronous left & right channel

in I2S mode and the beginning of a group of left & right channels in PCM mode |

| P27 | I2S1_SDI0_BT_PCM | AD6 | GPIO4_A6/I2S1_SDI0_d | IO | I2S/PCM serial data input [0] |

| P28 | I2S1_SDO0_BT_PCM | AC6 | GPIO4_A7/I2S1_SDO0_d | IO | I2S/PCM serial data output [0] |

I2S/PCM走线请注意:

- I2S/PCM在PCB布线上相邻的参考层要保持完整(相邻层要保持是同一个平面), 避免一些电源等其他信号的干扰, 且与同一层的其他的线有GND隔离

SPDIF

MYZR-RK3399_CB314 模块SPDIF接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P39 | PCIE_CLKREQ | AK1 | GPIO4_C5/SPDIF_TX_d | O | S/PDIFbiphase data ouput |

| P152 | RGMII_INT | D27 | GPIO3_C0/MAC_COL/UART3_CTSn/SPDIF_TX_u | O | S/PDIFbiphase data ouput |

多媒体接口

SDMMC接口

MYZR-RK3399_CB314 模块SDIO接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P87 | SDMMC0_CLK | V29 | GPIO4_B4/SDMMC0_CLKOUT/MUCJTAG_TCK_d | O | SDMMC card clock |

| P82 | SDMMC0_CMD | V25 | GPIO4_B5/SDMMC0_CMD/MCUJTAG_TMS_u | I/O | SDMMCcard command output and reponse input |

| P84 | SDMMC0_D0 | Y27 | GPIO4_B0/SDMMC0_D0/UART2A_RX_u | I/O | SDMMCcard data0 input and output |

| P83 | SDMMC0_D1 | Y26 | GPIO4_B1/SDMMC0_D1/UART2A_TX_u | I/O | SDMMCcard data1 input and output |

| P85 | SDMMC0_D2 | Y28 | GPIO4_B2/SDMMC0_D2/APJTAG_TCK_u | I/O | SDMMCcard data2 input and output |

| P88 | SDMMC0_D3 | U27 | GPIO4_B3/SDMMC0_D3/APJTAG_TMS_u | I/O | SDMMCcard data3 input and output |

| P86 | SDMMC0_DET_L | V28 | GPIO0_A7/SDMMC0_DET_u | I | SDMMCcard detect signal, a 0 represents presence of card |

SDIO接口

MYZR-RK3399_CB314 模块SDIO接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S39 | SDIO0_CLK | AF7 | GPIO2_D1/SDIO0_CLKOUT/TEST_CLKOUT1_u | O | SDIO card clock. |

| S37 | SDIO0_CMD | AH6 | GPIO2_D0/SDIO0_CMD_u | I/O | SDIO card command output and reponse input. |

| S36 | SDIO0_D0 | AD8 | GPIO2_C4/SDIO0_D0/SPI5_RXD_u | I/O | SDIOcard data0 input and output. |

| S38 | SDIO0_D1 | AK5 | GPIO2_C5/SDIO0_D1/SPI5_TXD_u | I/O | SDIOcard data1 input and output. |

| S40 | SDIO0_D2 | AG7 | GPIO2_C6/SDIO0_D2/SPI5_CLK_u | I/O | SDIOcard data2 input and output. |

| S41 | SDIO0_D3 | AE8 | GPIO2_C7/SDIO0_D3/SPI5_CSn0_u | I/O | SDIOcard data3 input and output. |

| S42 | BT_WAKE_L | AL4 | GPIO2_D2/SDIO0_DETN/PCIE_CLKREQn_u | I | SDIOcard detect signal, a 0 represents presence of card. |

| S27 | GPIO2_D4 | AF8 | GPIO2_D4/SDIO0_BKPWR_d | O | the back-end power supply for embedded device |

| S35 | GPIO2_D3 | AD9 | GPIO2_D3/SDIO0_PWREN_d | O | SDIOcard power-enable control signal |

| P91 | WIFI_HOST_WAKE_L | V31 | GPIO0_A3/SDIO0_WRPT_d | I | SDIOcard write protect signal, a 1 represents write is protected. |

| P103 | BT_HOST_WAKE_L | AA25 | GPIO0_A4/SDIO0_INTn_d | O | SDIOcard interrupt indication |

SDIO/SDMMC走线请注意:

- CLK单独走线,并做包地处理; DATA走线间距遵守3W规则; 并保证走线的参考面是一个连续完整的参考面,不被分割;

- 负载电容包括SD卡负载电容以及PCB负载电容两部分,其中SD卡的负载电容协议规定应该是小于10pF;

SDIO/SDMMC走线要求如表:

| 参数 | 要求 |

| Trace Impedance | 50Ω ±10% single ended |

| Max skew between data signal and clock | < 20ps |

| Max trace length | < 3.93 inchs |

| The minimum spacing of SDIO Signals | At least 2 times the width of SDIO trace. |

通讯接口

RGMII接口

MYZR-RK3399_CB314 模块RGMII接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P134 | RGMII_TXEN | H22 | GPIO3_B4/MAC_TXEN/UART1_RX_u | O | GMAC TX data enable |

| P135 | RGMII_TXD0 | D26 | GPIO3_A4/MAC_TXD0/SPI0_RXD_d | O | GMAC TX data0 |

| P136 | RGMII_TXD1 | G23 | GPIO3_A5/MAC_TXD1/SPI0_TXD_d | O | GMAC TX data1 |

| P137 | RGMII_TXD2 | F24 | GPIO3_A0/MAC_TXD2/SPI4_RXD_d | O | GMAC TX data2 |

| P138 | RGMII_TXD3 | H23 | GPIO3_A1/MAC_TXD3/SPI4_TXD_d | O | GMAC TX data3 |

| P139 | RGMII_TXCLK | E28 | GPIO3_C1/MAC_TXCLK/UART3_RTSn_u | O | RGMII TX clock output |

| P141 | RGMII_RXDV | C27 | GPIO3_B1/MAC_RXDV_d | I | GMAC RX data valid signal |

| P142 | RGMII_RXD0 | E26 | GPIO3_A6/MAC_RXD0/SPI0_CLK_u | I | GMAC RX data0 |

| P143 | RGMII_RXD1 | F27 | GPIO3_A7/MAC_RXD1/SPI0_CSn0_u | I | GMAC RX data1 |

| P144 | RGMII_RXD2 | E30 | GPIO3_A2/MAC_RXD2/SPI4_CLK_u | I | GMAC RX data2 |

| P145 | RGMII_RXD3 | E25 | GPIO3_A3/MAC_RXD3/SPI4_CSn0_u | I | GMAC RX data3 |

| P146 | RGMII_RXCLK | F25 | GPIO3_B6/MAC_RXCLK/UART3_RX_u | I | RGMII RX clock input |

| P148 | RGMII_CLK | G24 | GPIO3_B3/MAC_CLK/I2C5_SCL_u | I/O | RMII REC_CLK output or GMAC external clock input |

| P149 | RGMII_MDC | E29 | GPIO3_B0/MAC_MDC/SPI0_CSn1_u | O | GMAC management interface clock |

| P150 | RGMII_MDIO | G26 | GPIO3_B5/MAC_MDIO/UART1_TX_u | I/O | GMAC management interface data |

| P151 | RGMII_RST | B27 | GPIO3_B7/MAC_CRS/CIF_CLKOUTB/UART3_TX_u | I | PHY CRS signal |

| P152 | RGMII_INT | D27 | GPIO3_C0/MAC_COL/UART3_CTSn/SPDIF_TX_u | I | PHY Collision signal |

| P153 | RGMII_RXER | F23 | GPIO3_B2/MAC_RXER/I2C5_SDA_u | I | GMAC RX error signal |

RGMII走线请注意:

- PHY越靠近MYZR-RK3399_CB314 模块, EMI效果会越好,即RGMII走线越短EMI效果越好,必须小于15cm。

- RGMII_RXCL、RGMII_TXCLK必须包地处理

- 其它信号间距要满足3W布线原则

- RGMII_RXD[0:3],RGMII_RXDV,RGMII_RXCLK走线要等长处理,整条相差小于100mil,走线要尽量短,整条长度要小于15CM

- RGMII_TXD[0:3],RGMII_TXEN,RGMII_TXCLK走线要等长处理,整条相差小于100mil,走线要尽量短,整条长度要小于15CM

- 要有完整的参考面,不能和其它信号线直接平行布线。

USB接口

MYZR-RK3399_CB314 模块USB接口定义如下表所示:

- USB2.0—HOST0接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P75 | HOST0_DP | AB30 | HOST0_DP | I/O | USB 2.0 data DP |

| P76 | HOST0_DM | AB31 | HOST0_DM | I/O | USB 2.0 data DN |

- USB2.0—HOST1接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P77 | HOST1_DP | AA30 | HOST1_DP | I/O | USB 2.0 data DP |

| P78 | HOST1_DM | AA31 | HOST1_DM | I/O | USB 2.0 data DN |

- USB3.0—TYPEC0接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P43 | TYPEC0_SBU1_DC | AH17 | TYPEC0_AUXP_PD_PU | I/O | AUX pull-up/pull-down polarity reversal pins. For normal connectororientation,

there is a weak pull-down on aux_p wires and aweak pull-up on aux_m wire. These pins are used to reverse thisfor the flipped connector case. |

| P44 | TYPEC0_SBU2_DC | AG17 | TYPEC0_AUXM_PU_PD | ||

| P45 | TYPEC0_SBU2 | AL20 | TYPEC0_AUXM | I/O | AUX differential Tx/Rx serial data |

| P46 | TYPEC0_SBU1 | AK20 | TYPEC0_AUXP | ||

| P47 | TYPEC0_RX1N | AL21 | TYPEC0_RX1N | I/O | Lane 1 transmitter/receiver serial data - USB Rx or DP Tx.

RX1+/RX1- USB Type-C receptacle pins (B11/B10) |

| P48 | TYPEC0_RX1P | AK21 | TYPEC0_RX1P | ||

| P49 | TYPEC0_TX1P | AL22 | TYPEC0_TX1P | O | Lane 0 transmitter serial data - USB Tx or DP Tx.

TX+/TX1- USB Type-C receptacle pins (A2/A3) |

| P50 | TYPEC0_TX1N | AK22 | TYPEC0_TX1N | ||

| P51 | TYPEC0_RX2N | AL23 | TYPEC0_RX2N | I/O | Lane 2 transmitter/receiver serial data - USB Rx or DP Tx.

RX2+/RX2- USB Type-C receptacle pins (A11/A10) |

| P52 | TYPEC0_RX2P | AK23 | TYPEC0_RX2P | ||

| P53 | TYPEC0_TX2P | AL24 | TYPEC0_TX2P | O | Lane 3 transmitter serial data - USB Tx or DP Tx.

TX2+/TX2- USB Type-C receptacle pins (B2/B3) |

| P54 | TYPEC0_TX2N | AK24 | TYPEC0_TX2N | ||

| P55 | TYPEC0_DP | AG23 | TYPEC0_DP | I/O | USB 2.0 data DP |

| P56 | TYPEC0_DM | AH23 | TYPEC0_DM | I/O | USB 2.0 data DN |

| P57 | TYPEC0_U2VBUSDET | AK30 | TYPEC0_U2VBUSDET | I | VBUS BUMP into the PHY for VBUS monitor |

- USB3.0—TYPEC1接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P59 | USB3_SSRXN | AL25 | TYPEC1_RX1N | I/O | Lane 1 transmitter/receiver serial data - USB Rx or DP Tx.

RX1+/RX1- USB Type-C receptacle pins (B11/B10) |

| P60 | USB3_SSRXP | AK25 | TYPEC1_RX1P | ||

| P61 | USB3_SSTXP | AL26 | TYPEC1_TX1P | O | Lane 0 transmitter serial data - USB Tx or DP Tx.

TX+/TX1- USB Type-C receptacle pins (A2/A3) |

| P62 | USB3_SSTXN | AK26 | TYPEC1_TX1N | ||

| P63 | TYPEC1_RX2N | AL27 | TYPEC1_RX2N | I/O | Lane 2 transmitter/receiver serial data - USB Rx or DP Tx.

RX2+/RX2- USB Type-C receptacle pins (A11/A10) |

| P64 | TYPEC1_RX2P | AK27 | TYPEC1_RX2P | ||

| P65 | TYPEC1_TX2P | AL28 | TYPEC1_TX2P | O | Lane 3 transmitter serial data - USB Tx or DP Tx.

TX2+/TX2- USB Type-C receptacle pins (B2/B3) |

| P66 | TYPEC1_TX2N | AK28 | TYPEC1_TX2N | ||

| P67 | TYPEC1_SBU2 | AL29 | TYPEC1_AUXM | I/O | AUX differential Tx/Rx serial data |

| P68 | TYPEC1_SBU1 | AK29 | TYPEC1_AUXP | ||

| P69 | TYPEC1_SBU1_DC | AE24 | TYPEC1_AUXP_PD_PU | I/O | AUX pull-up/pull-down polarity reversal pins. For normal connectororientation,

there is a weak pull-down on aux_p wires and aweak pull-up on aux_m wire. These pins are used to reverse thisfor the flipped connector case. |

| P70 | TYPEC1_SBU2_DC | AF25 | TYPEC1_AUXM_PU_PD | ||

| P71 | TYPEC1_U2VBUSDET | AK31 | TYPEC1_U2VBUSDET | I | VBUS BUMP into the PHY for VBUS monitor |

| P72 | USB3_DP | AG24 | TYPEC1_DP | I/O | USB 2.0 data DP |

| P73 | USB3_DM | AH24 | TYPEC1_DM | I/O | USB 2.0 data DN |

USB 2.0走线要求如下:

- ESD器件靠近USB连接座放置;

- USB接口应尽量靠近芯片放置,以缩短走线距离;USB的信号走线必须严格遵循差分规则要求走线。走线拐角尽量用弧线或者钝角, 不能为直角或锐角

- 为抑制电磁辐射, USB建议在内层走线,并保证走线参考面是一个连续完整的参考面,不被分割,否则会造成差分线阻抗的不连续性并增加外部噪声对差分线的影响

- USB走线与其他信号需保持至少3W以上的间距

- USB走线与其他信号需保持至少3W以上的间距

- USB 2.0规范定义的电流为500mA,但是VBUS走线最好能承受1A的电流, 防止过流。如果是在使用USB充电的情况下, VBUS走线需能承受2.5A的电流;

USB2.0走线要求

| 参数 | 要求 |

| Trace Impedance | 90Ω ±10% differential |

| Max intra-pair skew | < 4ps |

| Max trace length on carrier board | < 6 inchs |

| Maximum allowed via | 6 |

USB 3.0走线基本参考《USB2.0设计》,另外请注意:

- USB 3.0工作模式为全双工,所以差分对SS_TX和SS_RX之间不需要做等长处理;

- USB 3.0协议要求在SS_TX线上增加100nF交流耦合电容(AC coupling capacitors),请对称放置电容并靠近USB连接座;

- SS_TX和SS_RX信号请严格按照差分对要求走线,保持走线间距一致,以保证走线阻抗的连续性;

- SS_TX和SS_RX信号在设置走线的延时时,请尽量靠近源端:即SS_RX信号靠近USB连接座,而SS_TX信号靠近RK3399。

- 为抑制电磁辐射,USB信号建议PCB内层走线,并保证走线参考面是一个连续完整的参考面,不被分割,否则会造成差分线阻抗的不连续性并引入外部噪声对的影响。如在PCB表层走线,请注意用地线做整组包地处理;差分对之间不需要伴随地走线;

RK3399 USB3.0走线要求

| 参数 | 要求 |

| Trace Impedance | 90Ω ±10% differential |

| Max intra-pair skew | < 4ps |

| Max trace length skew between RX and TX data pairs | < 1.6ns |

| Max trace length on carrier board | < 6inchs |

| AC coupling capacitors | 100nF ±20%, discrete 0201 package preferable |

| Minimum pair to pair spacing | > 3 times the width of the trace.

Try to increase Spacing between pairs whenever it is possible. |

| The minimum spacing between USB and other Signals | At least 3 times the width of USB trace. |

| Maximum allowed via | 4 |

PCIE接口

MYZR-RK3399_CB314 模块PCIE接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S122 | PCIE_RX0_P | AF30 | PCIE_RX0_P | I | PCIe differential data input signals |

| S123 | PCIE_RX0_N | AF31 | PCIE_RX0_N | I | PCIe differential data input signals |

| S125 | PCIE_TX0_P | AE30 | PCIE_TX0_P | O | PCIe differential data output signals |

| S126 | PCIE_TX0_N | AE31 | PCIE_TX0_N | O | PCIe differential data output signals |

| S116 | PCIE_RX1_P | AH30 | PCIE_RX1_P | I | PCIe differential data input signals |

| S117 | PCIE_RX1_N | AH31 | PCIE_RX1_N | I | PCIe differential data input signals |

| S119 | PCIE_TX1_P | AG30 | PCIE_TX1_P | O | PCIe differential data output signals |

| S120 | PCIE_TX1_N | AG31 | PCIE_TX1_N | O | PCIe differential data output signals |

| S138 | PCIE_RX2_P | AC27 | PCIE_RX2_P | I | PCIe differential data input signals |

| S139 | PCIE_RX2_N | AC28 | PCIE_RX2_N | I | PCIe differential data input signals |

| S141 | PCIE_TX2_P | AA27 | PCIE_TX2_P | O | PCIe differential data output signals |

| S142 | PCIE_TX2_N | AA28 | PCIE_TX2_N | O | PCIe differential data output signals |

| S131 | PCIE_RX3_P | AF27 | PCIE_RX3_P | I | PCIe differential data input signals |

| S132 | PCIE_RX3_N | AF28 | PCIE_RX3_N | I | PCIe differential data input signals |

| S134 | PCIE_TX3_P | AD27 | PCIE_TX3_P | O | PCIe differential data output signals |

| S135 | PCIE_TX3_N | AD28 | PCIE_TX3_N | O | PCIe differential data output signals |

| S128 | PCIE_RCLK_100M_P | AD31 | PCIE_RCLK_100M_P | O | 100MHz differential reference clock out for PCIe peripheral |

| S129 | PCIE_RCLK_100M_N | AD30 | PCIE_RCLK_100M_N | O | 100MHz differential reference clock out for PCIe peripheral |

PCIe走线要求如下:

- PCIe的TXn[0:3]、 RXn[0:3]可以根据产品的实际出线,调整差分对间线序, 如MYZR-RK3399_CB314的TX0连接到卡座的TX2; 但差分对内的P/N不可对调;

- AC耦合电容请靠近PCIe连接座放置;

- AC耦合电容建议使用0201封装,可以减少线路上的阻抗变化;

- PCIe信号建议并行走线,信号间不要有其他信号走线以及过孔;

- 在PCB表层走线请注意用地线做整组包地处理; 差分对之间不需要伴随地走线;

- TX和RX的差分对间是有lane-to-lane de-skew,所以不严格要求等长,可以通过tuning来实现;

PCIe线路要求:

| 参数 | 要求 |

| Trace Impedance | 100Ω ±10% differential |

| Max intra-pair skew | < 4ps |

| Max inter-pair skew | < 1.6ns |

| Maximum signal line length (coupled traces) TX and RX | < 14 inchs |

| AC coupling capacitors | 100nF ±20%, discrete 0201 package preferable |

| Minimum pair to pair spacing | > 3 times the width of the trace.Try to increase Spacing between pairs whenever it is possible. |

| Length matching between reference clock differential pairs REFCLK+ and REFCLK-(intra-pair) | < 4ps |

| The minimum spacing between PCIE and other Signals | At least 3 times the width of PCIE trace |

| Maximum allowed via | 4 |

UART接口

MYZR-RK3399_CB314 模块UART接口定义如下表所示:

- UART0接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S43 | UART0_CTS | AG8 | GPIO2_C2/UART0_CTSn_u | I | UART clear to send |

| S44 | UART0_RTS | AL5 | GPIO2_C3/UART0_RTSn_u | O | UART request to send |

| S45 | UART0_RXD | AE9 | GPIO2_C0/UART0_RX_u | I | UARTsearial data input |

| S46 | UART0_TXD | AH8 | GPIO2_C1/UART0_TX_u | O | UARTsearial data output |

- UART2接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P32 | UART2DBG_RX | AK2 | GPIO4_C3/UART2C_RX_u | I | UARTsearial data input |

| P33 | UART2DBG_TX | AJ4 | GPIO4_C4/UART2C_TX_u | O | UARTsearial data output |

I2C接口

MYZR-RK3399_CB314 模块I2C接口定义如下表所示:

- I2C1接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P29 | I2C1_SDA_1V8 | AG1 | GPIO4_A1/I2C1_SDA_u | I | I2C data line |

| P30 | I2C1_SCL_1V8 | Y6 | GPIO4_A2/I2C1_SCL_u | O | I2C serial clock line |

- I2C3接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S48 | I2C3_SDA_3V3 | AG6 | GPIO4_C0/I2C3_SDA/UART2B_RX_u | I | I2C data line |

| S49 | I2C3_SCL_3V3 | AL2 | GPIO4_C1/I2C3_SCL/UART2B_TX_u | O | I2C serial clock line |

- I2C4接口定义

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P101 | I2C4_SDA_1V8 | P31 | GPIO1_B3/I2C4_SDA_u | I | I2C data line |

| P102 | I2C4_SCL_1V8 | P30 | GPIO1_B4/I2C4_SCL_u | O | I2C serial clock line |

SPI接口

MYZR-RK3399_CB314 模块SPI接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| P111 | SPI1_TXD | R31 | GPIO1_B0/SPI1_TXD/UART4_TX_u | O | SPI serial data output |

| P112 | SPI1_RXD | P27 | GPIO1_A7/SPI1_RXD/UART4_RX_u | I | SPI serial data input |

| P113 | SPI1_CSN0 | P29 | GPIO1_B2/SPI1_CSn0/PMCU_JTAG_TMS_u | I/O | SPIfirstchip select signal,low active |

| P114 | SPI1_CLK | P28 | GPIO1_B1/SPI1_CLK/PMCU_JTAG_TCK_u | I/O | SPI serial clock |

PWM接口

MYZR-RK3399_CB314 模块PWM接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S32 | EDP_BL_PWM | AF5 | GPIO4_C2/PWM0/VOP0_PWM/VOP1_PWM_d | I/O | Pulse Width Modulation output |

| P37 | GPIO4_C6 | AL3 | GPIO4_C6/PWM1_d | I/O | Pulse Width Modulation output |

| P99 | DSI_BL_PWM | P25 | GPIO0_A6/PWM3A_IR_d | I/O | Pulse Width Modulation output, special design for IR receiver |

ADC接口

MYZR-RK3399_CB314 模块ADC接口定义如下表所示:

| 模块管脚号 | 模块管脚定义 | CPU 管脚号 | CPU 管脚定义 | I/O属性 | 功能描述 |

| S111 | ADC_IN0 | AG26 | ADC_IN0 | - | ADC input signal |

| S109 | ADC_IN1 | AH26 | ADKEY_IN | - | ADC input signal |

| S107 | ADC_IN2 | AG25 | HP_HOOK | - | ADC input signal |

| S114 | ADC_IN3 | AG28 | ADC_IN3 | - | ADC input signal |

| S113 | ADC_IN4 | AH27 | ADC_IN4 | - | ADC input signal |